## ABSTRACTION AND IMPLEMENTATION OF UNSTRUCTURED GRID ALGORITHMS ON MASSIVELY PARALLEL HETEROGENEOUS ARCHITECTURES

### István Zoltán Reguly

A thesis submitted for the degree of Doctor of Philosophy

Pázmány Péter Catholic University Faculty of Information Technology

SUPERVISORS:

András Oláh Ph.D.

Zoltán Nagy Ph.D.

Budapest, 2014

I would like to dedicate this work to my loving family.

## Acknowledgements

First of all, I am most grateful to my supervisors, Dr. András Oláh and Dr. Zoltán Nagy for their motivation, guidance, patience and support, as well as Prof. Tamás Roska for the inspiring and thought-provoking discussions that led me down this path. I thank Prof. Barna Garay for all his support, for being a pillar of good will and honest curiosity. I am immensely grateful to Prof. Mike Giles for welcoming me into his research group during my stay in Oxford, for guiding and supporting me, and for opening up new horizons.

I would like to thank all my friends and colleagues with whom I spent these past few years locked in endless debate; Csaba Józsa for countless hours of discussion, Gábor Halász, Helga Feiszthuber, Endre László, Gihan Mudalige, Carlo Bertolli, Fabio Luporini, Zoltán Tuza, János Rudan, Tamás Zsedrovits, Gábor Tornai, András Horváth, Dóra Bihary, Bence Borbély, Dávid Tisza and many others, for making this time so much enjoyable.

I thank the Pázmány Péter Catholic University, Faculty of Information Technology, for accepting me as a doctoral student and supporting me throughout, and the University of Oxford, e-Research Centre. I am thankful to Jon Cohen, Robert Strzodka, Justin Luitjens, Simon Layton and Patrice Castonguay at NVIDIA for the summer internship, while working on AmgX together I have learned a tremendous amount.

Finally, I will be forever indebted to my family, enduring my presence and my absence, and for being supportive all the while, helping me in every way imaginable.

### **Kivonat**

Lassan tíz éve már hogy a processzorok órajelének folyamatos növekedése - és ezzel a frekvencia-skálázódásnak köszönhető teljesítmény-növekedés - véget ért. Ez arra kényszerítette a gyártókat, hogy a számítási kapacitás elvárt növekedését más eszközökkel tartsák fenn. Megkezdődött a processzormagok számának növekedése, megjelentek a többszintű memória-architektúrák, a vezérlő áramkörök egyre bonyolultabbá váltak, új architektúrák, segédprocesszorok, programozási nyelvek és párhuzamos programozási technikák sokasága jelent meg. Ezek a megoldások a teljesítmény növelését, a hatékony programozhatóságot és az általános-célú felhasználást hivatottak biztosítani. A modern számítógépeken a számítási kapacitás ilyen módon való növelésének azonban a - tipikusan nagyméretű adatállományok gyors mozgatása szab határt. Ugyancsak korlátozó tényező, hogy a tudományos számítások területén dolgozók még mindig az évtizedekkel ezelőtt bevezetett jól bevált és tesztelt - programozási nyelveket és a bennük implementált módszereket kívánják használni. Ezektől a kutatóktól nem elvárható, hogy a saját szakterületükön kívül még az új hardverek és új programozási módszerek terén is mély ismeretekre tegyenek szert. Ugyanakkor ezek mélyreható ismerete nélkül egyre kevésbé aknázható ki az új hardverekben rejlő egyre magasabb potenciál. Az informatika-tudományok kutatói – köztük jelen dolgozat szerzője is – arra vállalkoznak, hogy az új hardverekkel és programozási módszerekkel kapcsolatos tapasztalataikat, eredményeiket olyan formába öntsék – illetve olyan absztrakciós szinteket definiáljanak – amely lehetővé teszi a más kutatási területeken dolgozók számára a folyamatosan növekedő számítási kapacitások hatékony kihasználását.

Hosszú évtizedek kutatásai ellenére a mai napig nincs olyan általános célú gépi fordító mely a régi, soros kódokat automatikusan képes lenne hatékonyan párhuzamosítani és a modern hardvereket hatékonyan kihasználva futtatni. Ezért az elmúlt időszak kutatásai egy-egy jól körülhatárolható probléma osztályt céloznak meg – sűrű és ritka lineáris algebra, strukturált és nem-strukturált térhálók, soktest problémák, Monte Carlo. Kutatásom céljának – a fenti törekvésekkel összhangban – a nem-strukturált térhálókon értelmezett algoritmusokat választottam. A nem-strukturált térhálókat rendszerint olyan parciális dif-

ferenciálegyenletek diszkretizált megoldásánál használják ahol az értelmezési tartomány szerkezete rendkívül bonyolult és a megoldás során különböző területeken különböző térbeli felbontásra van szükség. Tipikus mérnöki problémák – amelyek a nem-strukturált térhálók segítségével oldhatók meg – például a sekélyvízi szimulációk összetett partvonal mentén, vagy repülőgépek sugárhajtóművének áramlástani szimulációja a lapátok körül.

Kutatásomat a programozhatóság jelen kori nagy kihívásai motiválták: a párhuzamosság, az adatlokalitás, a teherelosztás és a hibatűrés. A disszertációm célja az, hogy bemutassa a nem-strukturált térhálókon értelmezett algoritmusokkal kapcsolatos kutatásaimat. Kutatásaim során különböző absztrakciós szintekről kiindulva vizsgálom a nem-strukturált térhálókkal kezelhető probléma megoldásokat. Ezen eredményeimet végül számítógépes kódra képeztem le, különös figyelmet szentelve a különböző absztrakciós szintek, a programozási modellek, a végrehajtási modellek és a hardver architektúrák összhangjának. Futtatási eredményekkel bizonyítom, hogy a modern heterogén architektúrákon jelenlévő párhuzamosság és memória-hierarchia hatékonyan kihasználható kutatási eredményeim felhasználásával.

Munkám első része a végeselem-módszert vizsgálja, amely egy magasabb absztrakciós szintet jelent a dolgozat többi részéhez viszonyítva. Ez lehetővé tette, hogy egy magasabb szinten alakítsam ezt a numerikus módszert a modern párhuzamos architektúrák adottságait figyelembe véve. Kutatásom megmutatja hogy a végeselem integráció különböző formulációival a memóriamozgatást és tárigényt csökkenteni lehet redundáns számításokért cserébe, mely az erőforrásokban szűk GPU-k esetén képes magas teljesítményt adni, még magasrendű elemek esetén is. Ezt követően megvizsgálom az adatstruktúrák problémáját, és megmutatom hogy egy, a végeselem-módszerekre felírt struktúra, hogyan használható fel a számítások különböző fázisaiban, valamint levezetem a memória-mozgatás mennyiségét, és mérések segítségével bizonyítom, hogy a GPU architektúrán magasabb teljesítményt képes elérni. Végül a ritka mátrixok és vektorok szorzatának párhuzamos architektúrákra való leképzését vizsgálom, megadok egy heurisztikát és egy gépi tanulási eljárást mely az optimális paramétereket képesek megtalálni általános ritka mátrixok esetén is.

A második részben – az első rész aránylag szűk kutatási területét kibővítettem, és – azokat az általános nem-strukturált térhálókon értelmezett algoritmusokat vizsgáltam, melyek az OP2 Domain Specific Language (DSL) [16] által definiált absztrakcióval leírhatóak. Ez az absztrakciós szint alacsonyabb, mint az első részben a végeselem-módszer esetében alkalmazott absztrakciós szint, ezért a numerikus módszerek magasabb szintű átalakítására itt nincs lehetőség. Ugyanakkor az OP2 ezen absztrakciója által lefedett te-

rület lényegesen szélesebb, így magában foglalja a végeselem-módszert, de emellett sok más algoritmust is, így például a véges térfogat módszert is. Kutatásom második része az OP2 absztrakciós szintjén definiált algoritmusok magas szintű transzformációival foglalkozik. Azt vizsgálja, hogy hogyan lehet a – tipikusan lineárisan megfogalmazott – számítási algoritmusok végrehajtását párhuzamos architektúrára transzformálni oly módon, hogy az adatlokalitás, a hibatűrés és az erőforrások kihasználtságának problémáját is megoldjuk. Ezen az absztrakciós szinten a kutatásaim még nem veszik figyelembe azt, hogy a végrehajtás milyen hardveren valósul meg. Ennek megfelelően a második rész eredményei megfelelő implementációs paraméterezéssel bármely végrehajtási környezetben felhasználhatóak. Elsőként egy teljesen automatizált algoritmust adok meg, mely képes megtalálni a végrehajtás során azt a pontot ahol az állapottér a legkisebb, elmenti azt, majd meghibásodás esetén képes attól a ponttól folytatni a számításokat. Ezek után általános megoldást adok a nem-struktúrált térhálókon értelmezett számítások olyan átszervezésére, mely az adatelérésekben lévő időbeli lokalitást javítja azzal, hogy egyszerre csak a probléma kisebb részén hajtja végre a számítások sorozatát - ú.n. "cache blocking" technikán alapulva. Megvizsgálom továbbá a mai heterogén rendszerek kihasználásának kérdését is, melyekben rendszerint több, eltérő tulajdonságokkal rendelkező hardver van. Megadok egy modellt a nem-struktúrált térhálón értelmezett algoritmusok heterogén végrehajtására, melyet az OP2-ben való implementációval igazolok.

Végül kutatásom harmadik része azzal foglalkozik, hogy az OP2 absztrakciós szintjén definiált algoritmusok miképp képezhetőek le különböző alacsonyabb szintű programozási nyelvekre, végrehajtási modellekre és hardver architektúrákra. Leképezéseket definiálok, amelyeknek segítségével a számításokat egymásra rétegzett párhuzamos programozási absztrakciókon keresztül a mai modern, heterogén számítógépeken optimálisan végre lehet hajtani, kihasználva az összetett memória-hierarchiát és a többszintű párhuzamosságot. Először bemutatom, hogy a végrehajtás miképp képezhető le GPU-kra, a CUDA programozási nyelv által, felhasználva a Single Instruction Multiple Threads (SIMT) modellt, valamint hogy hogyan lehet különböző optimalizációkat automatikusan kód generálás segítségével megvalósítani. Másodszor a CPU-szerű architektúrákra való leképzést mutatom meg, az egyes magokra OpenMP segítségével, valamint a magokon belül az AVX vektor utasításkészlet és a Single Instruction Multiple Data (SIMD) modell segítségével. A javasolt leképezések hatékonyságát áramlástani szimulációkon keresztül bizonyítom, többek közt a Rolls-Royce által repülőgép sugárhajtóművek tervezésére használt Hydra szoftver segítségével. Mindezt különböző hardvereken végzett mérések segítségével támasztom alá:

sokmagos CPU-kon, GPU-kon, az Intel Xeon Phi használatával valamint klasszikus és heterogén szuperszámítógépeken. Eredményeim azt bizonyítják, hogy a nem-strukturált térhálók probléma osztálya esetében a magas szintű absztrakciók módszere valóban képes a modern hardverekben rejlő teljesítmény automatizált kiaknázására és mindezek mellett hatékonyan leegyszerűsíti az algoritmikus problémák megfogalmazását és implementációját a felhasználók számára.

## Abstract

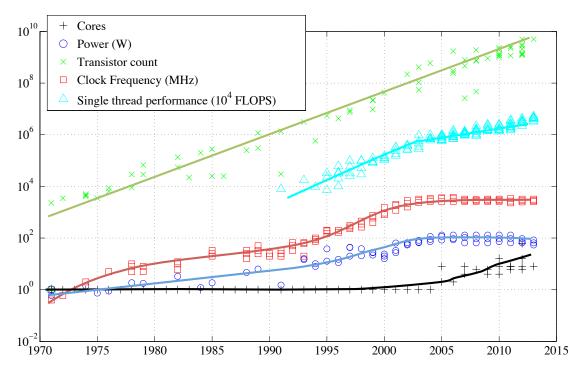

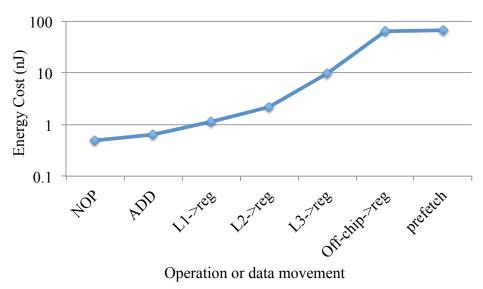

The last decade saw the long tradition of frequency scaling of processing units grind to a halt, and efforts were re-focused on maintaining computational growth by other means; such as increased parallelism, deep memory hierarchies and complex execution logic. After a long period of "boring productivity", a host of new architectures, accelerators, programming languages and parallel programming techniques appeared, all trying to address different aspects of performance, productivity and generality. Computations have become cheap and the cost of data movement is now the most important factor for performance, however in the field of scientific computations many still use decades old programming languages and techniques. Domain scientists cannot be expected to gain intimate knowledge of the latest hardware and programming techniques that are often necessary to achieve high performance, thus it is more important than ever for computer scientists to take on some of this work; to come up with ways of using new architectures and to provide a synthesis of these results that can be used by domain scientists to accelerate their research.

Despite decades of research, there is no universal auto-parallelising compiler that would allow the performance portability of codes to modern and future hardware, therefore research often focuses on specific domains of computational sciences, such as dense or sparse linear algebra, structured or unstructured grid algorithms, N-body problems and many others. For my research, I have chosen to target the domain of unstructured grid computations; these are most commonly used for the discretisation of partial differential equations when the computational domain is geometrically complex and the solution requires different resolution in different areas. Examples would include computational fluid dynamics simulations around complex shorelines or the blades of an aircraft turbine.

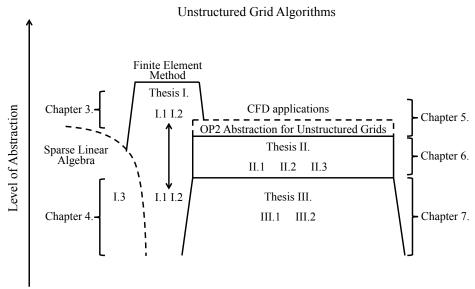

The aim of this dissertation is to present my research into unstructured grid algorithms, starting out at different levels of abstraction where certain assumptions are made, which in turn are used to reason about and apply transformations to these algorithms. They are then mapped to computer code, with a focus on the dynamics between the programming model, the execution model and the hardware; investigating how the parallelism and the

deep memory hierarchies available on modern heterogeneous hardware can be utilised optimally. In short, my goal is to address some of the programming challenges in modern computing; parallelism, locality, load balancing and resilience, in the field of unstructured grid computations.

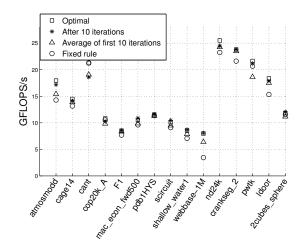

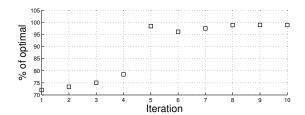

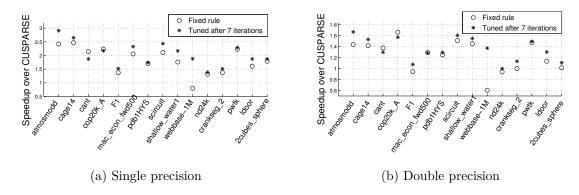

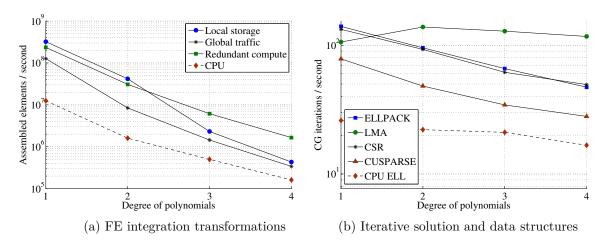

The first part of my research studies the Finite Element Method (FEM), therefore starts at a relatively high level of abstraction, allowing a wide range of transformations to the numerical methods involved. I show that by differently formulating the FE integration, it is possible to trade off computations for communications or temporary storage; mapping these to the resource-scarce Graphical Processing Unit (GPU) architecture, I demonstrate that a redundant compute approach is scalable to high order elements. Then, data storage formats and their implications on the algorithms are investigated, I demonstrate that a FEM-specific format is highly competitive with classical approaches, deriving data movement requirements, and showing its advantages in a massively parallel setting. Finally, I parametrise the execution of the sparse-matrix product (spMV) for massively parallel architectures, and present a constant-time heuristic as well as a machine learning algorithm to determine the optimal values of these parameters for general sparse matrices.

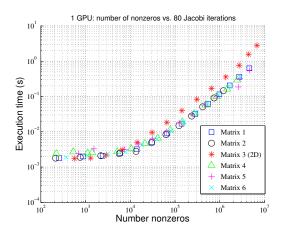

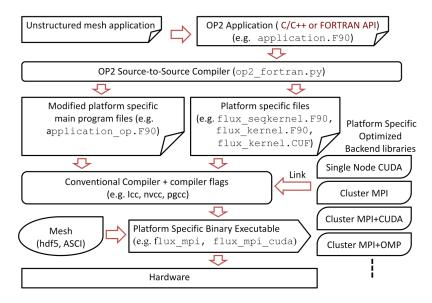

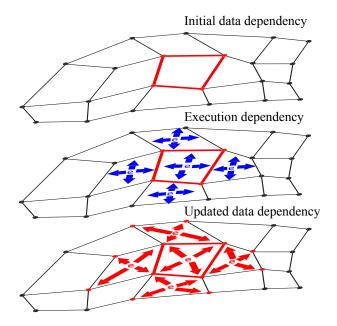

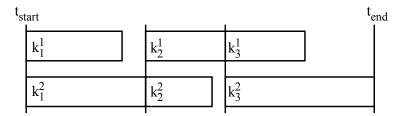

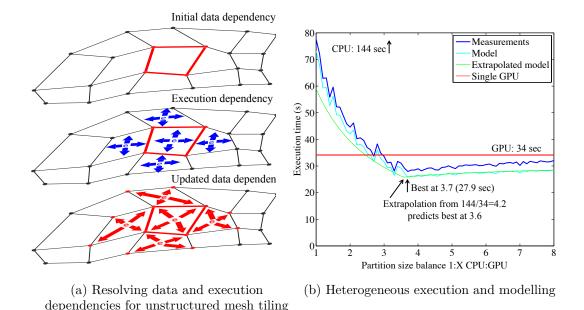

Following the first part that focused on challenges in the context of the finite element method, I broaden the scope of my research by addressing general unstructured grid algorithms that are defined through the OP2 domain specific library [16]. OP2's abstraction for unstructured grid computations covers the finite element method, but also others such as the finite volume method. The entry point here, that is the level of abstraction, is lower than that of the FEM, thus there is no longer control over the numerical method, however it supports a much broader range of applications. The second part of my research investigates possible transformations to the execution of computations defined through the OP2 abstraction in order to address the challenges of locality, resilience and load balancing at a higher level, that is not concerned with the exact implementation. I present a fully automated checkpointing algorithm that is capable of locating the point during execution where the state space is minimal, save data, and in the case of a failure automatically fastforward execution to the point of the last backup. Furthermore, I give an algorithm for the redundant-compute tiling, or cache-blocking, execution of general unstructured grid computations that fully automatically reorganises computations across subsequent computational loops in order to improve the temporal locality of data accesses. I also address the issue of utilisation in modern heterogeneous systems where different hardware with different performance characteristics are present. I give a model for such heterogeneous cooperative execution of unstructured grid algorithms and validate it with an implementation in OP2.

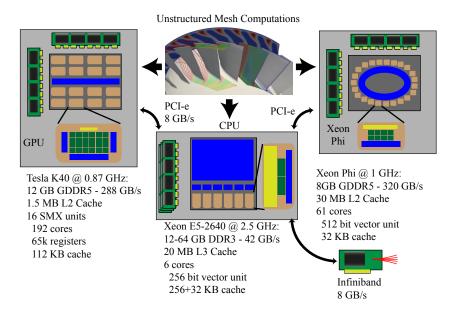

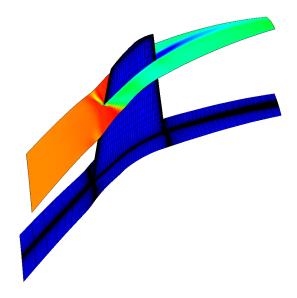

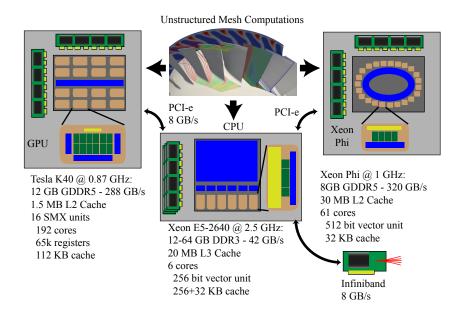

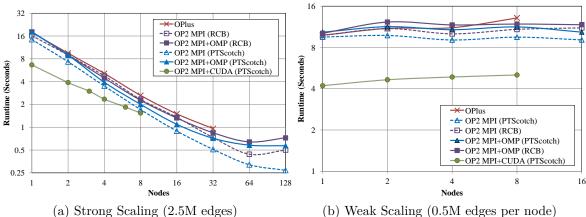

Finally, the third part of my research presents results on how an algorithm defined once through OP2 can be automatically mapped to a range of contrasting programming languages, execution models and hardware. I show how execution is organised on large scale heterogeneous systems, utilising layered programming abstractions, across deep memory hierarchies and many levels of parallelism. First, I discuss how execution is mapped to GPUs through CUDA and the Single Instruction Multiple Threads (SIMT) model, deploying a number of optimisations to execution patterns and data structures fully automatically through code generation. Second, I present a mapping to CPU-like architectures, utilising OpenMP or MPI for Simultaneous Multithreading as well as AVX vector instructions for Single Instruction Multiple Data (SIMD) execution. These techniques are evaluated on computational fluid dynamics simulations, including the industrial application Rolls-Royce Hydra, on a range of different hardware, including GPUs, multi-core CPUs, the Intel Xeon Phi co-processor and distributed memory supercomputers combining CPUs and GPUs. My work demonstrates the viability of the high-level abstraction approach and its benefits in terms of performance and developer productivity.

## Abbreviations

- AVX Advanced Vector Extensions

- AoS Array of Structures

- CG Conjugate Gradient

- CPU Central Processing Unit

- CSP Communicating Sequential Processes

- CSR Compressed Sparse Row

- CUDA Compute Unified Device Architecture

- DSL Domain Specific Language

- DDR Double Data Rate (RAM type)

- ECC Error Checking & Correcting

- FEM Finite Element Method

- GDDR Graphics Double Data Rate (RAM type)

- GMA Global Matrix Assembly

- GPU Graphical Processing Unit

- **HPC** High Performance Computing

- IMCI Initial Many Core Instructions

- LMA Local Matrix Assembly

- MPI Message Passing Interface

- NUMA Non-Uniform Memory Access

- OPlus Oxford Parallel Library for Unstructured Grids

- OP2 The second version of OPlus

- QPI Quick Path Interconnect

- RAM Random Access Memory

- RISC Reduced Instruction Set Computing

- SIMD Single Instruction Multiple Data

- SIMT Single Instruction Multiple Threads

- SMT Simultaneous Multithreading

- SM Scalar Multiprocessor

- ${\rm SMX}$  Scalar Multiprocessor in Kepler-generation GPUs

- SoA Structure of Arrays

- spMV sparse Matrix-Vector multiplication

- TBB Threading Building Blocks

## Contents

| 1 | Intr | oducti                                                  | on                                                                                                                                                                                                                               | 1                                                     |

|---|------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

|   | 1.1  | Hardw                                                   | rare evolution                                                                                                                                                                                                                   | 1                                                     |

|   |      | 1.1.1                                                   | Processing units                                                                                                                                                                                                                 | 1                                                     |

|   |      | 1.1.2                                                   | Memory                                                                                                                                                                                                                           | 3                                                     |

|   |      | 1.1.3                                                   | Putting it together                                                                                                                                                                                                              | 4                                                     |

|   | 1.2  | Implic                                                  | ations to Programming Models                                                                                                                                                                                                     | 7                                                     |

|   | 1.3  | Motiva                                                  | ations for this research                                                                                                                                                                                                         | 10                                                    |

|   | 1.4  | The st                                                  | ructure of the dissertation                                                                                                                                                                                                      | 11                                                    |

| 2 | Har  | dware                                                   | Architectures Used                                                                                                                                                                                                               | 14                                                    |

|   | 2.1  | CPU a                                                   | architectures                                                                                                                                                                                                                    | 15                                                    |

|   | 2.2  | The In                                                  | tel Xeon Phi                                                                                                                                                                                                                     | 16                                                    |

|   | 2.3  | NVIDI                                                   | IA GPUs                                                                                                                                                                                                                          | 17                                                    |

| 3 | Fin  | ite Ele                                                 | ment Algorithms and Data Structures                                                                                                                                                                                              | 21                                                    |

|   | 3.1  | The F                                                   | inite Element Method                                                                                                                                                                                                             | 21                                                    |

|   |      | 1110 1                                                  |                                                                                                                                                                                                                                  | 21                                                    |

|   | 3.2  |                                                         | Element Assembly                                                                                                                                                                                                                 | 23                                                    |

|   | 3.2  |                                                         |                                                                                                                                                                                                                                  |                                                       |

|   | 3.2  | Finite                                                  | Element Assembly                                                                                                                                                                                                                 | 23                                                    |

|   | 3.2  | Finite 3.2.1                                            | Element Assembly                                                                                                                                                                                                                 | 23<br>24                                              |

|   | 3.2  | Finite 3.2.1 3.2.2 3.2.3                                | Element Assembly                                                                                                                                                                                                                 | <ul><li>23</li><li>24</li><li>25</li><li>27</li></ul> |

|   |      | Finite 3.2.1 3.2.2 3.2.3                                | Element Assembly                                                                                                                                                                                                                 | 23<br>24<br>25<br>27<br>28                            |

|   |      | Finite<br>3.2.1<br>3.2.2<br>3.2.3<br>Finite             | Element Assembly                                                                                                                                                                                                                 | 23<br>24<br>25<br>27<br>28<br>29                      |

|   |      | Finite<br>3.2.1<br>3.2.2<br>3.2.3<br>Finite<br>3.3.1    | Element Assembly  Dirichlet boundary conditions  Algorithmic transformations  Parallelism and Concurrency  Element Data Structures  Global Matrix Assembly (GMA)                                                                 | 23<br>24<br>25<br>27<br>28<br>29<br>30                |

|   |      | Finite 3.2.1 3.2.2 3.2.3 Finite 3.3.1 3.3.2             | Element Assembly  Dirichlet boundary conditions  Algorithmic transformations  Parallelism and Concurrency  Element Data Structures  Global Matrix Assembly (GMA)  The Local Matrix Approach (LMA)                                | 23<br>24<br>25<br>27<br>28<br>29<br>30<br>31          |

|   |      | Finite 3.2.1 3.2.2 3.2.3 Finite 3.3.1 3.3.2 3.3.3 3.3.4 | Element Assembly  Dirichlet boundary conditions  Algorithmic transformations  Parallelism and Concurrency  Element Data Structures  Global Matrix Assembly (GMA)  The Local Matrix Approach (LMA)  The Matrix-Free Approach (MF) | 23<br>24<br>25<br>27<br>28<br>29<br>30<br>31<br>31    |

| 4 | The                   | FEM            | on GPUs                                                    | <b>37</b> |

|---|-----------------------|----------------|------------------------------------------------------------|-----------|

|   | 4.1                   | Impler         | mentation of algorithms for GPUs                           | 37        |

|   |                       | 4.1.1          | Related work                                               | 38        |

|   | 4.2                   | Experi         | imental setup                                              | 38        |

|   |                       | 4.2.1          | Test problem                                               | 38        |

|   |                       | 4.2.2          | Test hardware and software environment                     | 39        |

|   |                       | 4.2.3          | Test types                                                 | 39        |

|   |                       | 4.2.4          | CPU implementation                                         | 40        |

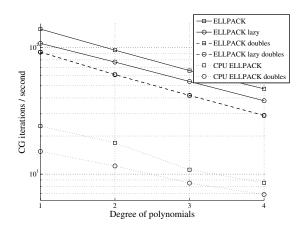

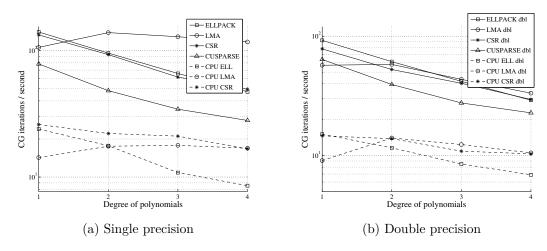

|   | 4.3                   | Perfor         | mance of algorithmic transformations of the FE integration | 41        |

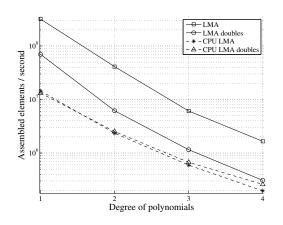

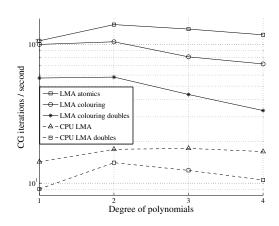

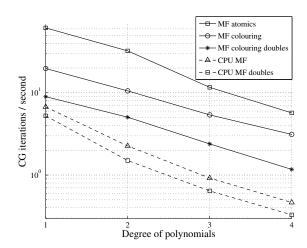

|   | 4.4                   | Perfor         | mance with different data structures                       | 42        |

|   |                       | 4.4.1          | The CSR layout                                             | 42        |

|   |                       | 4.4.2          | The ELLPACK layout                                         | 43        |

|   |                       | 4.4.3          | The LMA method                                             | 44        |

|   |                       | 4.4.4          | The Matrix-free method                                     | 46        |

|   |                       | 4.4.5          | Bottleneck analysis                                        | 47        |

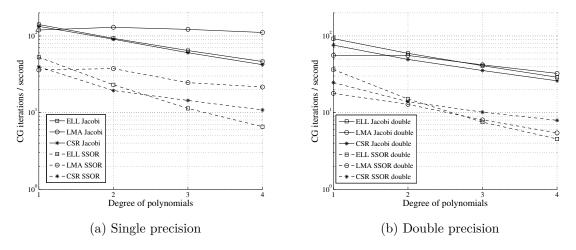

|   |                       | 4.4.6          | Preconditioning                                            | 51        |

|   | 4.5                   | Genera         | al sparse matrix-vector multiplication on GPUs             | 53        |

|   |                       | 4.5.1          | Performance Evaluation                                     | 58        |

|   |                       | 4.5.2          | Run-Time Parameter Tuning                                  | 64        |

|   |                       | 4.5.3          | Distributed memory spMV                                    | 67        |

|   | 4.6                   | Summ           | ary and associated theses                                  | 70        |

| 5 | $\mathbf{Th}\epsilon$ | o <b>OP2</b> . | Abstraction for Unstructured Grids                         | 72        |

|   | 5.1                   | The O          | P2 Domain Specific library                                 | 72        |

|   | 5.2                   |                | irfoil benchmark                                           |           |

|   | 5.3                   |                | - tsunami simulations                                      |           |

|   | 5.4                   |                | - turbomachinery simulations                               |           |

| 6 | Hig                   | h-Leve         | el Transformations with OP2                                | 80        |

| • | 6.1                   |                | pointing to improve resiliency                             |           |

|   | 0.1                   | 6.1.1          | An example on Airfoil                                      |           |

|   | 6.2                   |                | to improve locality                                        |           |

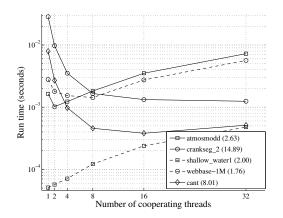

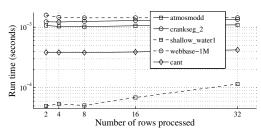

|   | 6.3                   | _              | ogeneous execution                                         |           |

|   | 0.0                   | 6.3.1          | Performance evaluation                                     |           |

|   | 6.4                   |                | ary and associated theses                                  |           |

|   | 0.4                   | Dumm           | .ary and abbordance incocs                                 | 90        |

| 7  | Map  | oping t | to Hardware with OP2                       | 95         |

|----|------|---------|--------------------------------------------|------------|

|    | 7.1  | Constr  | ructing multi-level parallelism            | 95         |

|    |      | 7.1.1   | Data Dependencies                          | 97         |

|    | 7.2  | Mappi   | ng to Graphical Processing Units           | 98         |

|    |      | 7.2.1   | Performance and Optimisations              | 100        |

|    | 7.3  | Mappi   | ng to CPU-like architectures               | 107        |

|    |      | 7.3.1   | Vectorising unstructured grid computations | 112        |

|    |      | 7.3.2   | Vector Intrinsics on CPUs                  | 115        |

|    |      | 7.3.3   | Vector Intrinsics on the Xeon Phi          | 117        |

|    | 7.4  | Summ    | ary and associated theses                  | 120        |

| 8  | Con  | clusio  | ns                                         | 122        |

| 9  | The  | ses of  | the Dissertation                           | 124        |

|    | 9.1  | Metho   | ds and Tools                               | 124        |

|    | 9.2  | New se  | cientific results                          | 125        |

|    | 9.3  | Applic  | eability of the results                    | 132        |

| 10 | App  | endix   |                                            | <b>134</b> |

|    | 10.1 | Mappi   | ng to distributed, heterogeneous clusters  | 134        |

|    |      | 10.1.1  | Strong Scaling                             | 135        |

|    |      |         | Weak Scaling                               |            |

|    |      |         | Performance Breakdown at Scale             |            |

# List of Figures

| 1.1 | Evolution of processor characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Cost of data movement across the memory hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4  |

| 1.3 | Structure of the dissertation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12 |

| 2.1 | The challenge of mapping unstructured grid computations to various hard-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|     | ware architectures and supercomputers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 14 |

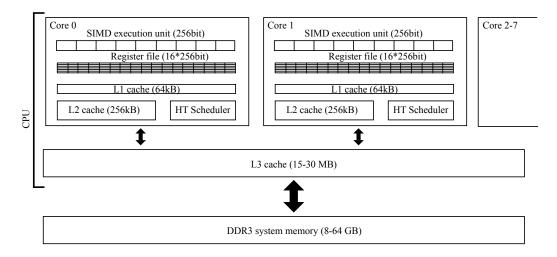

| 2.2 | Simplified architectural layout of a Sandy Bridge generation server CPU $$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 15 |

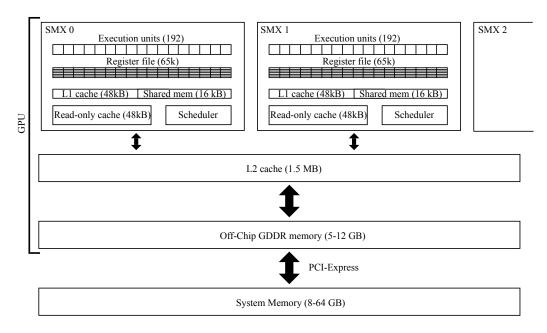

| 2.3 | Simplified architectural layout of a Kepler-generation GPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 18 |

| 2.4 | An example of a CUDA execution grid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 19 |

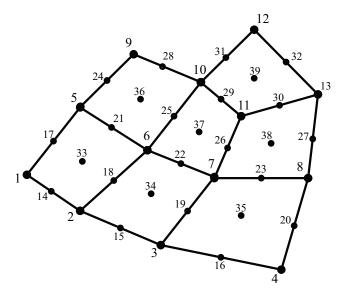

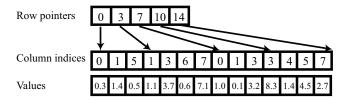

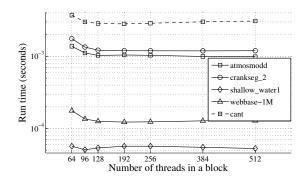

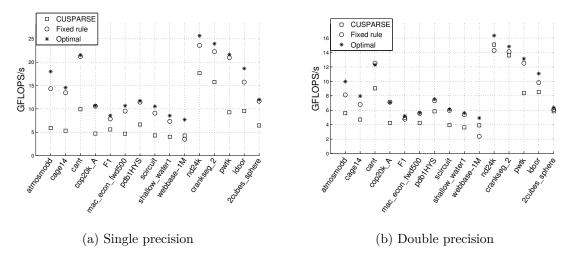

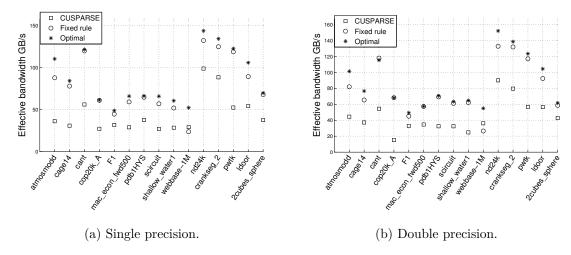

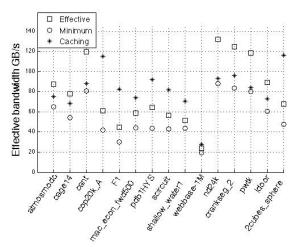

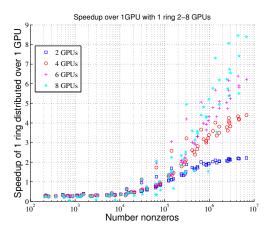

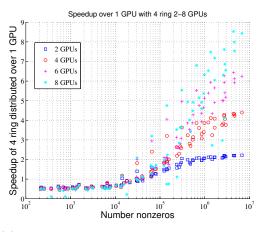

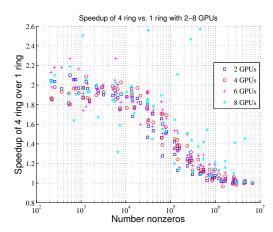

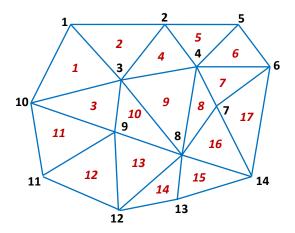

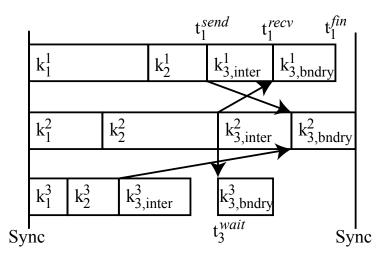

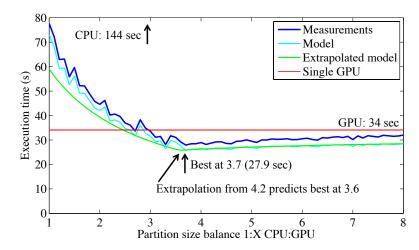

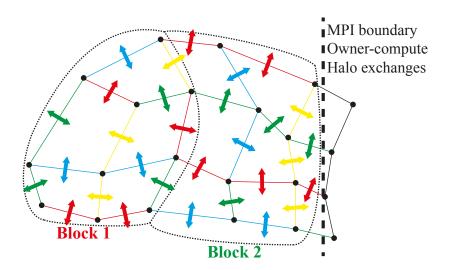

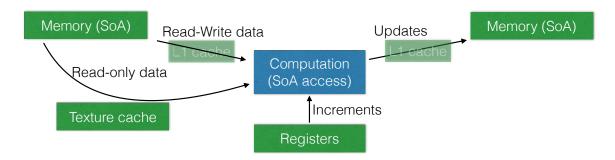

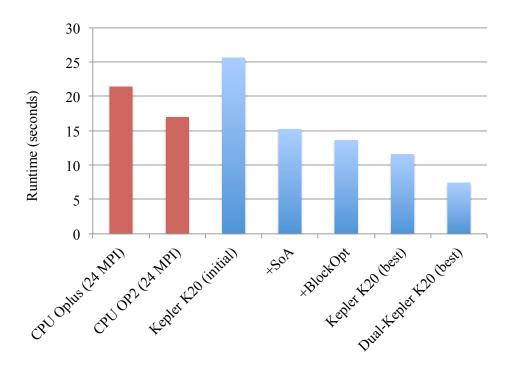

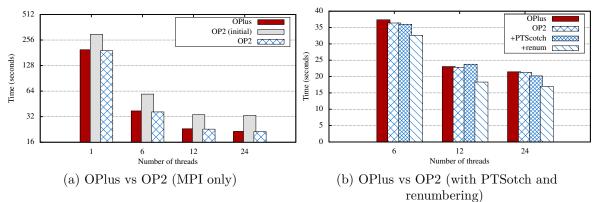

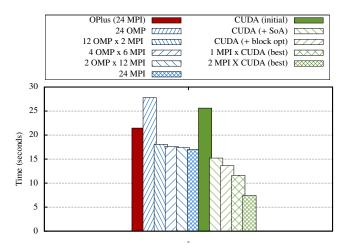

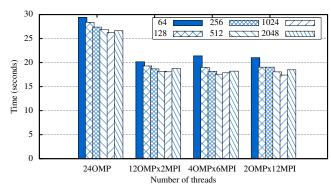

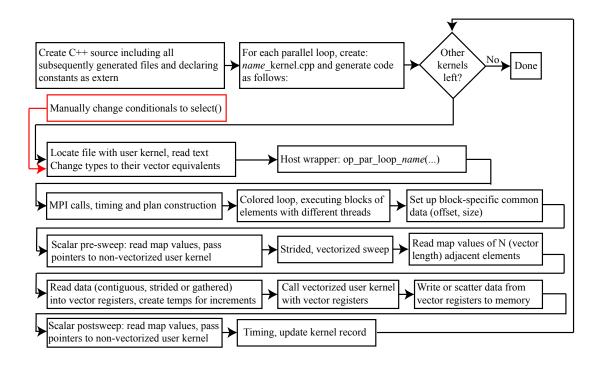

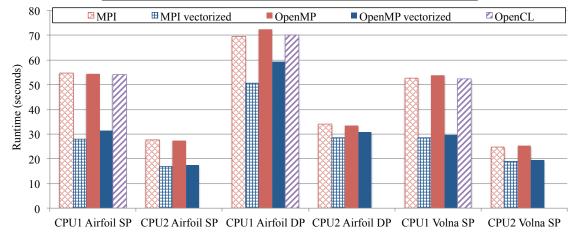

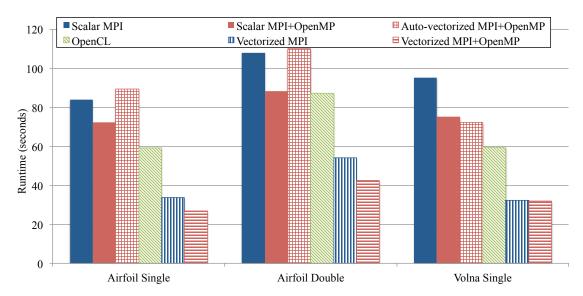

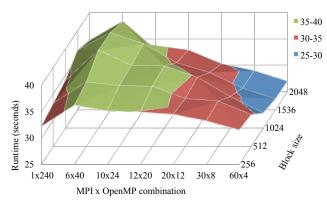

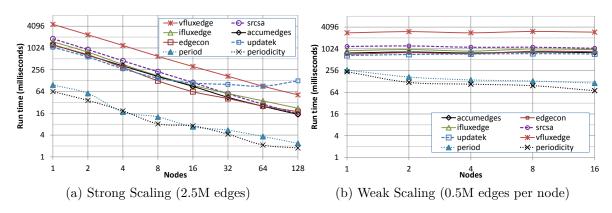

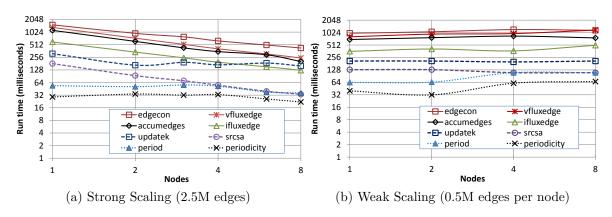

| 3.1 | An example of a quadrilateral finite element mesh, with degrees of freedom                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |