## Design and Implementation of High-Performance Computing Algorithms for Wireless MIMO Communications

Thesis submitted for the degree of Doctor of Philosophy

Csaba Máté Józsa, M.Sc.

## Supervisors

Géza Kolumbán, D.Sc.

Doctor of the Hungarian Academy of Sciences and

Péter Szolgay, D.Sc.

Doctor of the Hungarian Academy of Sciences

Pázmány Péter Catholic University

Faculty of Information Technology and Bionics

Multidisciplinary Doctoral School of Sciences and Technology

Budapest, 2015

I would like to dedicate this work to my loving family.

## Acknowledgements

First of all, I am most grateful to my supervisors, *Profs. Géza Kolumbán* and *Péter Szolgay* for their motivation, guidance, patience and support.

I owe my deepest gratitude to *Prof. Tamás Roska* for the inspiring and thought-provoking discussions and for opening up new horizons. I deeply thank *Prof. Árpád Csurgay* and *Dr. András Oláh* for the motivation and encouragement, giving me the strength to go on.

I am immensely grateful to *Prof. Antonio M. Vidal* for inviting me to his research group at the Institute of Telecommunications and Multimedia Applications (iTEAM) of the Polytechnic University of Valencia and sharing with me his wide experience in computational mathematics every time I needed it. I am very grateful to *Prof. Alberto González*, *Dr. Gema Piñero* and *Dr. Francisco J. Martínez-Zaldívar* for their generous advice and help in the field of wireless communications and showing me the strength of the team work.

I would like to thank all my friends and colleagues with whom I spent these past few years Dóra Bihary, Bence Borbély, Zsolt Gelencsér, Antal Hiba, Balázs Jákli, András Laki, Endre László, Norbert Sárkány, István Reguly, János Rudán, Zoltán Tuza, Tamás Fülöp, András Horváth, Miklós Koller, Mihály Radványi, Ádám Rák, Attila Stubendek, Gábor Tornai, Tamás Zsedrovits, Ádám Balogh, Ádám Fekete, László Füredi, Kálmán Tornai, Ákos Tar, Dávid Tisza, Gergely Treplán, József Veres, András Bojárszky, Balázs Karlócai, Tamás Krébesz. Special thanks go to István Reguly for more than a decade of friendship and of continuous collaboration.

Thanks also to my colleagues at the iTEAM: Emanuel Aguilera, Jose A. Belloch, Fernando Domene, Laura Fuster Pablo Gutiérrez, Jorge Lorente, Luis Maciá, Amparo Martí, Carla Ramiro for all the good moments spent together while working at the lab.

I thank the Pázmány Péter Catholic University, Faculty of Information Technology and Bionics, for accepting me as a doctoral student and supporting me throughout grants TÁMOP-4.2.1/B-11/2/KMR-2011-0002 and TÁMOP-4.2.2/B-10/1-2010-0014.

#### DOI:10.15774/PPKE.ITK.2015.010

Finally, I will be forever indebted to my parents  $Enik\~o$  and M'at'e, brother Istv'an, and grandparents B"obe, 'Eva, M'arton for enduring my presence and my absence, and for being supportive all the while, helping me in every way imaginable.

Last, but not least, I would like to express my sincere gratitude to my wife  $Ildik\acute{o}$ , who offered me unconditional love and support throughout the course of this thesis.

## **Kivonat**

A vezeték nélküli kommunikációban a többantennás (MIMO) rendszerek azzal kerültek a figyelem középpontjába, hogy jelentős adatátviteli sebesség növekedést és jobb lefedettséget tudnak elérni a sávszélesség és az adóteljesítmény növelése nélkül. A jobb teljesítmény ára a hardverelemek és a jelfeldolgozó algoritmusok megnövekedett komplexitása. A legújabb kutatási eredmények azt igazolják, hogy a masszívan párhuzamos architektúrák (MPA-k) számos számításigényes feladatot képesek hatékonyan megoldani. Kutatásom célja, hogy a többantennás vezeték nélküli kommunikáció területén megjelenő magas komplexitású jelfeldolgozási feladatokat a modern MPA-k segítségével, mint például az általános célú grafikus feldolgozó egységek (GP-GPU-k) vagy sokmagos központi egységek (CPU), hatékonyan megoldjak.

MIMO rendszerekben az optimális Maximum Likelihood (ML) becslésen alapuló detekció komplexitása exponenciálisan növekszik az antennák számával és a moduláció rendjével. A szférikus detektor (SD) jelentősen csökkentve a lehetséges megoldások keresési terét hatékonyan oldja meg az ML detekciós problémát. Az SD algoritmus fő hátránya a szekvenciális jellegében rejlik, ezért futtatása MPA-kon nem hatékony.

Kutatásom első részében bemutatom a párhuzamos szférikus detekciós (PSD) algoritmust, mely kiküszöböli az SD algoritmus hátrányait. A PSD algoritmus egy új fakeresési algoritmust valósít meg, ahol a párhuzamosságot egy hibrid, szélességi és mélységi fakeresés hatékony kombinációja biztosítja. Az algoritmus minden keresési szinten egy út metrikán alapuló párhuzamos rendezést hajt végre. A PSD algoritmus paraméterei segítségével képes meghatározni a memória igényét és párhuzamosságának mértékét ahhoz, hogy hatékonyan ki tudja használni számos párhuzamos architektúra erőforrásait. A PSD algoritmus MPA-ra való leképezését a rendelkezésre álló szálak számától függő, párhuzamos építőelemek segítségével valósítom meg. Továbbá, a párhuzamos építőelemek alapján a PSD algoritmus egy GP-GPU architektúrán kerül implementálásra. A csúcsteljesítmény eléréséhez több párhuzamossági szint meghatározására és különböző ütemezési stratégiákra van szükség.

Többfelhasználós kommunikációs rendszerek esetén, ha a bázisállomás több antennával rendelkezik a térbeli diverzitás akkor is kihasználható, ha a mobil állomásoknak csak egy antennájuk van. Mivel a mobil állomások számára nem minden kommunikációs csatorna ismert, az összes jelfeldolgozási feladat a bázisállomásra hárul, ilyen például a szimbólumok előkódolása, mely a felhasználok közötti interferenciát szünteti meg. Ha a bázisállomás számára a mobil állomások visszacsatolják a csatorna paramétereit, akkor a lineáris és nemlineáris előkódolási technikák teljesítménye tovább javítható rácsredukciós algoritmusok alkalmazásával. Több kutatás is bizonyította, hogy a rácsredukcióval támogatott lineáris és nemlineáris előkódolás jelentősen csökkenti a bithibaarányt a rácsredukcióval nem támogatott előkódoláshoz képest. Továbbá számos kutatás megmutatta, hogy a rácsredukció a lineáris és nemlineáris detekció teljesítményét is tudja fokozni. A rácsredukció során létrejövő új bázis kondíciószáma és az ortogonalitási hiba mérséklése lehetővé teszi, hogy a kevésbé komplex lineáris detekciós algoritmusok is teljes rendű diverzitást érjenek el.

A rácsredukciós algoritmusok komplexitása a bázis méretétől függ. Mivel a rácsredukciót a MIMO rendszerek csatorna mátrixán kell végrehajtani, a rácsredukció komplexitása és ezzel együtt a feldolgozási idő kritikussá válhat nagy MIMO rendszerek esetén. Mivel a rácsredukció, pontosabban a polinomrendű Lenstra-Lenstra-Lovász (LLL) rácsredukciós algoritmus fontos szerepet játszik a vezeték nélküli kommunikáció területén, a kutatásom második részében az LLL algoritmus teljesítményének további fokozása a célom.

A párhuzamos All-Swap LLL (AS-LLL) algoritmus esetén a Gram-Schmidt együtthatók minden mátrix oszlopcsere és méret csökkentési procedúra után aktualizálásra kerülnek. Mivel a gyakori oszlopcsere és méret csökkentés több alkalommal módosítja a Gram-Schmidt együtthatók értékét, ezért egyes együtthatók aktualizálása feleslegessé válik. A költségcsökkentett AS-LLL (CR-AS-LLL) algoritmus megtervezésével megmutattam, hogy jelentős komplexitás csökkenés érhető el, ha csak azok a Gram-Schmidt együtthatók kerülnek aktualizálásra, melyek az LLL feltételek kiértékelésében vesznek részt. Ha már nincs végrehajtandó oszlopcsere és méret csökkentési procedúra a fennmaradó együtthatók aktualizálásra kerülnek. Bemutatom egy GP-GPU architektúrára való hatékony leképezését a CR-AS-LLL algoritmusnak, ahol egy kétdimenziós CUDA blokk szálai hajtják végre a redukciót.

Nagyobb méretű mátrixok esetén a párhuzamosság több szintje is kiaknázható. A módosított blokk LLL (MB-LLL) algoritmus egy kétszintű párhuzamosságot valósít meg. A magasabb párhuzamossági szinten a blokk redukciós koncepciót alkalmazom, míg az

#### DOI:10.15774/PPKE.ITK.2015.010

alacsonyabb szinten az egyes blokkok párhuzamos feldolgozását a CR-AS-LLL algoritmus valósítja meg.

A költség csökkentett MB-LLL algoritmusban a számítási komplexitás tovább csökkenthető, ha engedélyezett az első LLL feltétel lazítása az almátrixok rácsredukciója során. A CR-MB-LLL algoritmust leképeztem egy heterogén architektúrára és a teljesítőképességet összehasonlítottam egy dinamikus párhuzamosságot támogató GP-GPU és többmagos CPU leképezéssel. A heterogén architektúra alkalmazása lehetővé teszi a kernelek dinamikus ütemezését és lehetővé válik több CUDA folyam párhuzamos használata.

Az elért kutatási eredményeim azt mutatják, hogy a MPA-k fontos szerepet fognak játszani a jövőbeli jelfeldolgozó algoritmusok esetén és az aktuális jelfeldolgozó algoritmusok szekvenciális összetevőinek korlátozásai sok esetben megszüntethetők az algoritmusok teljes újratervezésével, ezáltal jelentős teljesítmény növekedés érhető el.

## Abstract

Multiple—input multiple-output (MIMO) systems have attracted considerable attention in wireless communications because they offer a significant increase in data throughput and link coverage without additional bandwidth requirement or increased transmit power. The price that has to be paid is the increased complexity of hardware components and algorithms. Recent results have proved that massively parallel architectures (MPAs) are able to solve computationally intensive tasks in a very efficient manner. The goal of my research was to solve computationally demanding signal processing problems in the field of wireless communications with modern MPAs, such as General-Purpose Graphics Processing Units (GP-GPUs), and multi-core Central Processing Units (CPUs).

The complexity of the optimal hard-output Maximum Likelihood (ML) detection in MIMO systems increases exponentially with the number of antennas and modulation order. The Sphere Detector (SD) algorithm solves the problem of ML detection by significantly reducing the search space of possible solutions. The main drawback of the SD algorithm is in its sequential nature, consequently, running it MPAs is very inefficient.

In the first part of my research I present the Parallel Sphere Detector (PSD) algorithm that overcomes the drawbacks of the SD algorithm. The PSD implements a novel tree search, where the algorithm parallelism is assured by a hybrid tree search based on the efficient combination of depth-first search and breadth-first search algorithms. A path metric based parallel sorting is employed at each intermediate stage. The PSD algorithm is able to adjust its memory requirements and extent of parallelism to fit a wide range of parallel architectures. Mapping details for MPAs are presented by giving the details of thread dependent, highly parallel building blocks of the algorithm. I show how it is possible to give a GP-GPU mapping of the PSD algorithm based on the parallel building blocks. In order to achieve high-throughput, several levels of parallelism are introduced, and different scheduling strategies are considered.

When a multiple-antenna base station (BS) is applied to multi-user communication, spatial diversity can be achieved even if the mobile stations (MSs) are not equipped

with multiple antennas. However, since the MSs do not know other users' channels, the entire processing task must be done at the BS, especially symbol precoding to cancel multi-user interference. Assuming channel information is sent back by all the MSs to the BS, a promising technique that can be applied for both linear and non-linear precoding techniques is the lattice reduction (LR) of the channel matrix. It was shown that the bit error rate (BER) performance of LR-aided precoding is significantly decreased compared to non-LR-aided precoding. Recent research shows that the performance of linear and non-linear detectors can be improved when used in conjuction with LR techniques. The improved condition number and orthogonality defect of the reduced lattice basis achieves full diversity order even with less-complex linear detection methods.

However, the computational cost of LR algorithms depending on the matrix dimensions could be high, and can become critical for large MIMO arrays. Since LR, and more explicitly the polynomial-time Lenstra-Lenstra-Lovász (LLL) lattice reduction algorithm plays an important role in the field of wireless communications, in the second part of my research the focus is to further improve the performance of the LLL algorithm.

In the original parallel All-Swap LLL (AS-LLL) algorithm after every size reduction or column swap the Gram-Schmidt coefficients are updated. However, a lot of unnecessary computations are performed because the frequent size reductions and column swaps change the value of the Gram-Schmidt coefficients several times. With the Cost-Reduced AS-LLL (CR-AS-LLL) algorithm I showed that by updating only those Gram-Schmidt coefficients that are involved in the evaluation of the LLL conditions, a significant complexity reduction is achieved. The remaining coefficients are updated after no more swaps and size reductions have to be performed. I present a GP-GPU mapping of the CR-AS-LLL algorithm where the work is distributed among the threads of a two-dimensional thread block, resulting in the coalesced access of the high-latency global memory, and the elimination of shared memory bank conflicts.

For larger matrices it is possible to exploit several levels of parallelism. The Modified-Block LLL (MB-LLL) implements a two-level parallelism: a higher-level, coarse-grained parallelism by applying a block-reduction concept, and a lower-level, fine-grained parallelism is implemented with the CR-AS-LLL algorithm.

The computational complexity of the MB-LLL is further reduced in the Cost-Reduced MB-LLL (CR-MB-LLL) algorithm by allowing the relaxation of the first LLL condition while executing the LR of sub-matrices, resulting in the delay of the Gram-Schmidt coefficients update and by using less costly procedures during the boundary checks. A

#### DOI:10.15774/PPKE.ITK.2015.010

mapping of the CR-MB-LLL on a heterogeneous platform is given and it is compared with mappings on a dynamic parallelism enabled GP-GPU and a multi-core CPU. The mapping on the heterogeneous architecture allows a dynamic scheduling of kernels where the overhead introduced by host-device communication is hidden by the use of several Compute Unified Device Architecture (CUDA) streams.

The achieved results of my research show that MPAs will play an important role in future signal processing tasks and limitations imposed by the sequential components of existing signal processing algorithms can be eliminated with the complete redesign of these algorithms achieving significant performance improvement.

## Abbreviations

APP A Posteriori Probability

ARBF Adapting Reduced Breadth-First search

AS-LLL All-Swap LLL algorithm

ASD Automatic Sphere Detector

ASIC Application-Specific Integrated Circuit

AWGN Additive White Gaussian Noise

BER Bit Error Rate

BFS Breadth-First Search

BLAST Bell Laboratories Layered Space-Time architecture

BS Base Station

CDF Cumulative Distribution Function

CDI Channel Distribution Information

CLPS Closest Lattice Point Search

CPU Central Processing Unit

CR-AS-LLL Cost-Reduced AS-LLL algorithm

CR-MB-LLL Cost-Reduced MB-LLL algorithm

CSI Channel State Information

CSIR CSI at the Receiver

CSIT CSI at the Transmitter

CUDA Compute Unified Device Architecture

DFS Depth-First Search

DP Dynamic Parallelism

DSP Digital Signal Processor

EEP Expand and Evaluate Pipeline

FBF Full-Blown Breadth-First search

FLOP/s Floating-Point Operations per Second

FP Fincke-Phost

#### DOI:10.15774/PPKE.ITK.2015.010

FPGA Field Programmable Gate Array

FSD Fixed-Complexity Sphere Detector

GP-GPU General-Purpose Graphics Processing Unit

HKZ Hermite-Korkine-Zolotareff algorithm

ILS Integer Least Squares

LDPC Low-Density Parity-Check Codes

LLL Lenstra-Lenstra-Lovász algorithm

LORD Layered Orthogonal Lattice Detector

LR Lattice Reduction

LRAP Lattice-Reduction-Aided Precoding

MB-LLL Modified-Block LLL algorithm

MIMD Multiple Instruction, Multiple Data

MIMO Multiple-Input Multiple-Output

MISD Multiple Instruction, Single Data

MISO Multiple-Input Single-Output

ML Maximum Likelihood

MMSE Minimum Mean Square Error

MPA Massively Parallel Architecture

MPI Message Passing Interface

MS Mobile Station

NUMA Non-Uniform Memory Access

OFDM Orthogonal Frequency-Division Multiplexing

OpenMP Open Multi-Processing

PE Processing Element

PER Packet Error Rate

PSD Parallel Sphere Detector

QAM Quadrature Amplitude Modulation

SD Sphere Detector

SE Schnorr-Euchner

SIC Successive Interference Cancellation

SIMD Single Instruction, Multiple Data

SIMT Single Instruction, Multiple Threads

SINR Signal-to-Interference plus Noise Ratio

SISD Single Instruction, Single Data

#### DOI:10.15774/PPKE.ITK.2015.010

SISO Single-Input Single-Output SM(X) Streaming Multiprocessor

SMP Symmetric Multiprocessor

SNR Signal-to-Noise Ratio

SSFE Selective Spanning Fast Enumeration

STC Space-Time Coding

SVD Singular Value Decomposition

TB Thread Block

THP Tomlinson-Harashima Precoding

UMA Uniform Memory Access

VLSI Very Large Scale Integration

ZF Zero-Forcing

## Contents

| 1 | Intr | roduction                                                                         | 1  |

|---|------|-----------------------------------------------------------------------------------|----|

|   | 1.1  | Motivation and scope                                                              | 1  |

|   | 1.2  | Thesis outline                                                                    | 3  |

| 2 | Hig  | h-performance computing architectures and programming models                      | 6  |

|   | 2.1  | Flynn's taxonomy of parallel architectures                                        | 6  |

|   | 2.2  | Overview of parallel programming models                                           | 11 |

|   |      | 2.2.1 The CUDA programming model                                                  | 12 |

| 3 | Ove  | erview of MIMO communications                                                     | 14 |

|   | 3.1  | Benefits of MIMO systems                                                          | 14 |

|   | 3.2  | MIMO system model                                                                 | 15 |

|   | 3.3  | MIMO capacity                                                                     | 17 |

| 4 | MI   | MO detection methods and algorithms                                               | 20 |

|   | 4.1  | Introduction                                                                      | 20 |

|   | 4.2  | MIMO detectors classification                                                     | 21 |

|   | 4.3  | Linear detectors                                                                  | 23 |

|   |      | 4.3.1 Zero-forcing detection                                                      | 23 |

|   |      | 4.3.2 Minimum mean square error detection                                         | 25 |

|   | 4.4  | Successive interference cancellation detectors                                    | 28 |

|   |      | 4.4.1 Successive interference cancellation detection concept                      | 28 |

|   |      | $4.4.2  \hbox{The Vertical Bell Laboratories Layered Space-Time architecture}  .$ | 29 |

|   | 4.5  | Maximum likelihood detection                                                      | 32 |

|   | 4.6  | Maximum likelihood tree-search based detectors                                    | 33 |

|   |      | 4.6.1 The Sphere Detector algorithm                                               | 33 |

|   |      | 4.6.1.1 General description of the Sphere Detector algorithm                      | 33 |

|   |     |         | 4.6.1.2     | The Fincke-Phost and Schnorr-Euchner enumeration               |    |

|---|-----|---------|-------------|----------------------------------------------------------------|----|

|   |     |         |             | strategies                                                     | 37 |

|   |     |         | 4.6.1.3     | Complexity analysis of the Sphere Detector algorithm $$ . $$ . | 39 |

|   |     | 4.6.2   | The Aut     | tomatic Sphere Detector algorithm                              | 43 |

|   | 4.7 | Non-n   | naximum     | likelihood tree-search based detectors                         | 44 |

|   |     | 4.7.1   | K-Best S    | Sphere Detector algorithm                                      | 45 |

|   |     | 4.7.2   | Hybrid 1    | tree-search detectors                                          | 45 |

|   |     |         | 4.7.2.1     | The Adaptive Reduced Breadth-First Search algorithm $$ .       | 48 |

|   |     |         | 4.7.2.2     | The Fixed-Complexity Sphere Detector algorithm $$              | 50 |

|   | 4.8 | The P   | arallel Sp  | here Detector algorithm                                        | 51 |

|   |     | 4.8.1   | Design o    | objectives of the Parallel Sphere Detector algorithm           | 52 |

|   |     | 4.8.2   | General     | description of the Parallel Sphere Detector algorithm          | 52 |

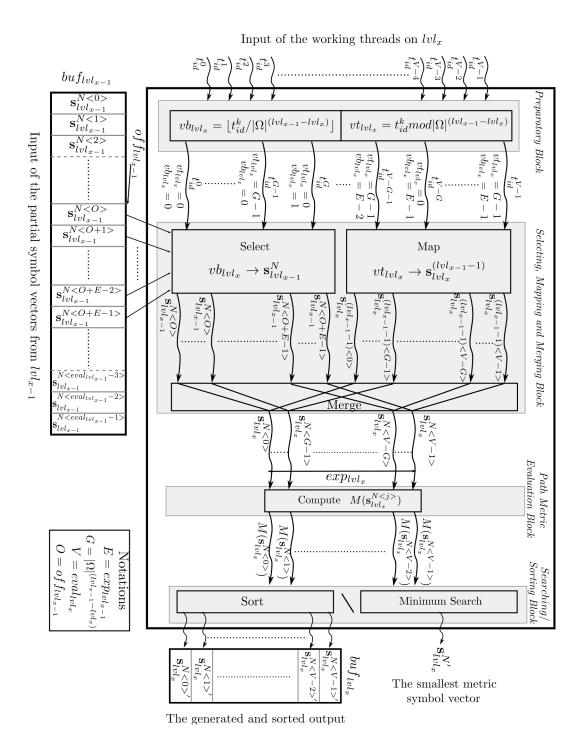

|   |     | 4.8.3   | The mai     | in building blocks of the Expand and Evaluate pipeline         | 59 |

|   |     |         | 4.8.3.1     | Preparatory block                                              | 60 |

|   |     |         | 4.8.3.2     | Selecting, mapping and merging block                           | 62 |

|   |     |         | 4.8.3.3     | Path metric evaluation block                                   | 63 |

|   |     |         | 4.8.3.4     | Searching or sorting block                                     | 63 |

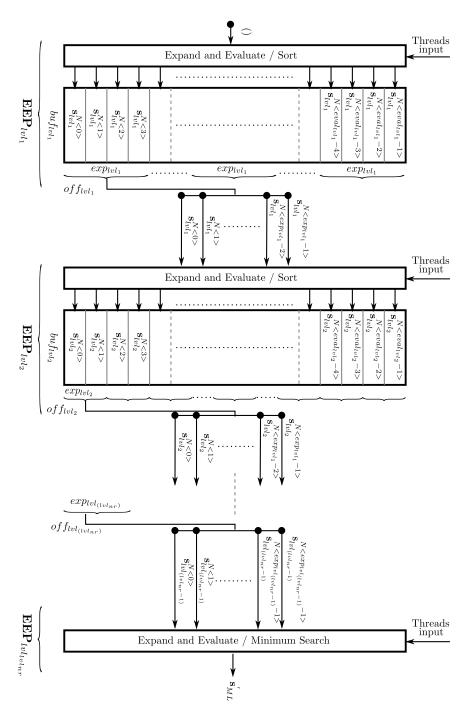

|   |     |         | 4.8.3.5     | Application of the Expand and Evaluate pipeline                | 63 |

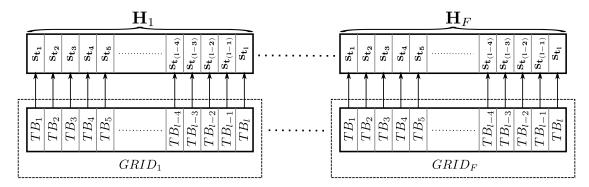

|   |     | 4.8.4   | Levels o    | f parallelism and CUDA mapping details                         | 65 |

|   |     | 4.8.5   | Perform     | ance evaluation of the Parallel Sphere Detector algorithm .    | 68 |

|   |     |         | 4.8.5.1     | Average detection throughput and scalability                   | 69 |

|   |     |         | 4.8.5.2     | Preprocessing of the channel matrix                            | 72 |

|   |     |         | 4.8.5.3     | Average complexity per thread                                  | 74 |

|   |     |         | 4.8.5.4     | Comparison of detection throughput and bit error rate          |    |

|   |     |         |             | performance                                                    | 76 |

|   | 4.9 | Concl   | usion       |                                                                | 80 |

| 5 | Lat | tice re | duction     | and its applicability to MIMO systems                          | 82 |

|   | 5.1 | Introd  | luction     |                                                                | 82 |

|   | 5.2 | Lattic  | e reduction | on preliminaries                                               | 84 |

|   | 5.3 | Lattic  | e reduction | on algorithms                                                  | 90 |

|   |     | 5.3.1   | Hermite     | -Korkine-Zolotareff and Minkowski lattice basis reduction .    | 91 |

|   |     | 5.3.2   | The Len     | stra-Lenstra-Lovász lattice basis reduction                    | 93 |

|   |     | 5.3.3   | Seysen's    | lattice basis reduction                                        | 96 |

|   | 5.4 | Lattic  | e reduction | on aided signal processing                                     | 98 |

|   |     |         |             |                                                                |    |

|   |     | 5.4.1   | Lattice reduction aided MIMO detection                               | 98         |

|---|-----|---------|----------------------------------------------------------------------|------------|

|   |     | 5.4.2   | Lattice reduction aided MISO precoding                               | 101        |

|   | 5.5 | Lattic  | e reduction parallelization strategies                               | 104        |

|   |     | 5.5.1   | The All-Swap lattice reduction algorithm                             | 105        |

|   |     | 5.5.2   | The parallel block reduction concept                                 | 105        |

|   | 5.6 | Paralle | el lattice reduction algorithms and their mapping to parallel archi- |            |

|   |     | tecture | es                                                                   | 106        |

|   |     | 5.6.1   | The Cost-Reduced All-Swap LLL lattice reduction algorithm $$         | 106        |

|   |     | 5.6.2   | The Modified-Block LLL lattice reduction algorithm                   | 112        |

|   |     | 5.6.3   | The Cost-Reduced Modified-Block LLL lattice reduction algorithm      | 114        |

|   |     | 5.6.4   | Evaluation results                                                   | 116        |

|   | 5.7 | Conclu  | asion                                                                | 122        |

| 6 | The | eses of | the Dissertation                                                     | <b>124</b> |

|   | 6.1 | Metho   | ods and tools                                                        | 124        |

|   | 6.2 | New s   | cientific results                                                    | 126        |

|   | 6.3 | Applic  | eability of the results                                              | 135        |

# List of Figures

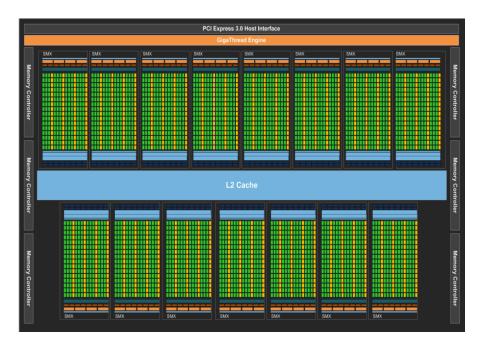

| 2.1  | The block diagram of the GK110 Kepler architecture                                            | 8  |

|------|-----------------------------------------------------------------------------------------------|----|

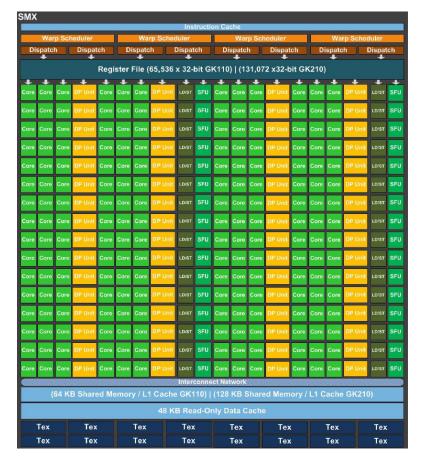

| 2.2  | The $\mathrm{GK}110/\mathrm{GK}210$ Kepler streaming multiprocessor (SMX) unit archi-         |    |

|      | tecture                                                                                       | 9  |

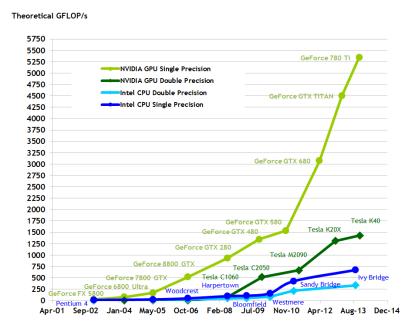

| 2.3  | The evolution of theoretical floating-point operations per second                             |    |

|      | (FLOP/s) for CPU and GP-GPU architectures                                                     | 10 |

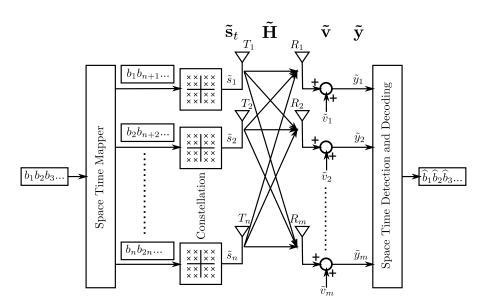

| 3.1  | $\ensuremath{MIMO}$ system architecture with n transmitter and m receiver antennas            | 15 |

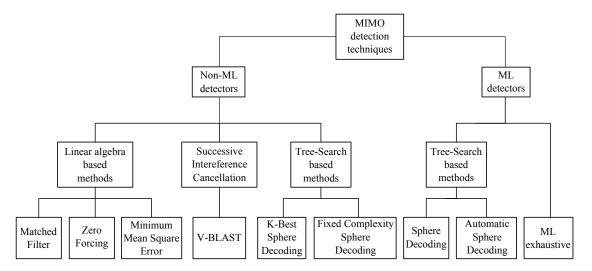

| 4.1  | Classification of spatial multiplexing MIMO detection methods                                 | 22 |

| 4.2  | Bit error rate performance comparison of linear detectors for $4\times4$ MIMO                 |    |

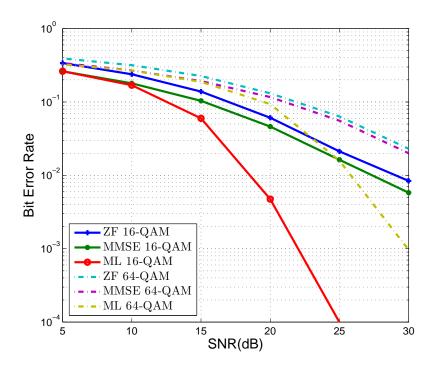

|      | systems with 16 and 64-QAM symbol constellations                                              | 27 |

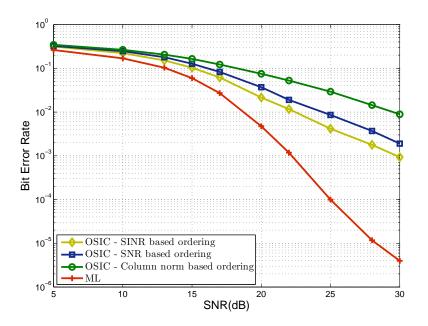

| 4.3  | Vertical BLAST detection bit error rate performance comparison for $4\times 4$                |    |

|      | $\operatorname{MIMO}$ with 16-QAM symbol constellation considering (i) SINR, (ii) SNR         |    |

|      | and (iii) column norm based ordering                                                          | 31 |

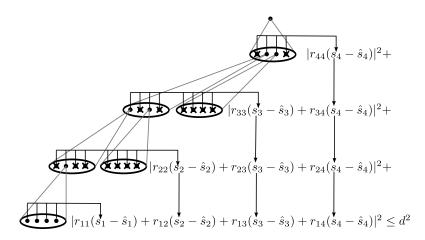

| 4.4  | Branch and bound search with the Sphere Detector algorithm                                    | 37 |

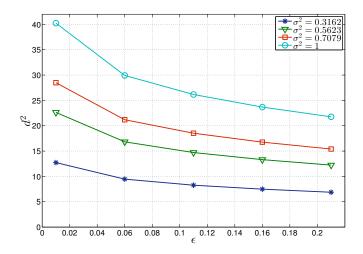

| 4.5  | The radius size of the bounding sphere for different $\varepsilon$ and $\sigma^2$ parameters. | 40 |

| 4.6  | The expected number $E_p$ of nodes visited for a $4 \times 4$ MIMO with $ \Omega  = 4$        |    |

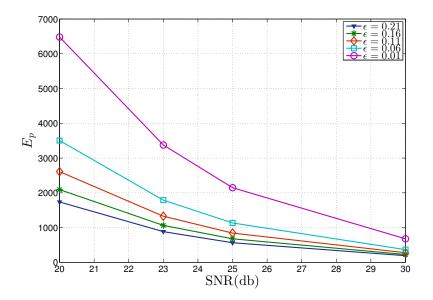

|      | and $\epsilon = 0.01, 0.06, 0.11, 0.16, 0.21$ parameter values                                | 42 |

| 4.7  | Bit error rate performance of the K-Best detector for $K=1,2,4,8,12,16$                       |    |

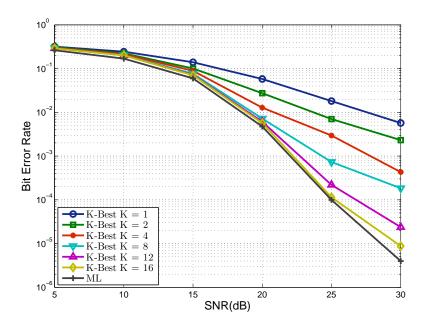

|      | in a 4 × 4 MIMO system with 16-QAM symbol constellation                                       | 47 |

| 4.8  | Bit error rate performance of the K-Best detector for $K=1,2,4,8,16,32$                       |    |

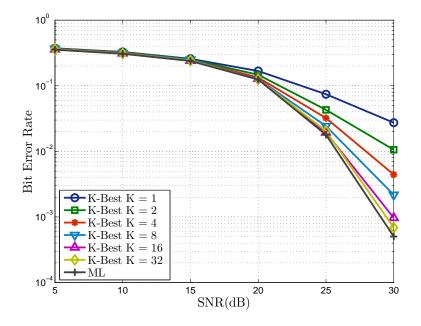

|      | in a 4 × 4 MIMO system with 64-QAM symbol constellation                                       | 47 |

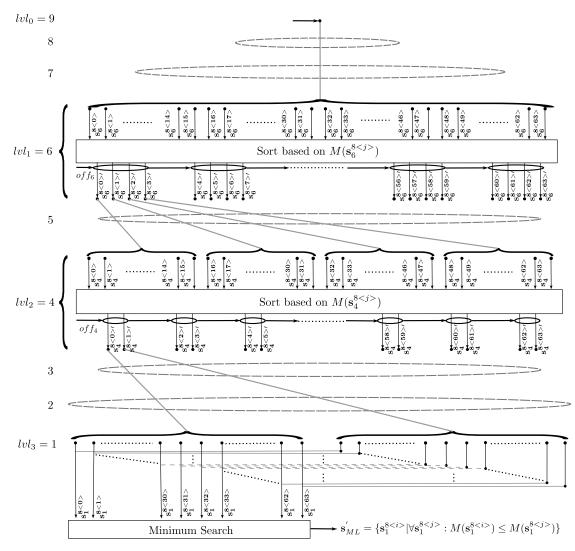

| 4.9  | The hybrid tree traversal of the Parallel Sphere Detector algorithm for a                     |    |

|      | $4 \times 4$ MIMO system with $ \Omega  = 4$                                                  | 55 |

| 4.10 | The block diagram of the Expand and Evaluate pipeline                                         | 61 |

| 4.11 | The iterative application of the Expand and Evaluate pipeline implement-                      |    |

|      | ing the Parallel Sphere Detector algorithm                                                    | 64 |

| 4.12        | Equally distributed computing load with the direct biding of the thread                        |    |

|-------------|------------------------------------------------------------------------------------------------|----|

|             | blocks and symbol vectors                                                                      | 66 |

| 4.13        | Dynamically distributed computing load with the dynamic biding of the                          |    |

|             | thread blocks and symbol vectors                                                               | 66 |

| 4.14        | A simplified thread block scheduling model on a streaming multiprocessor.                      | 67 |

| 4.15        | The scheduling of kernels using the single stream and multiple stream                          |    |

|             | execution models                                                                               | 67 |

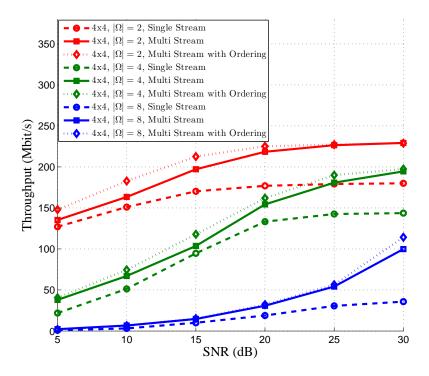

| 4.16        | The Parallel Sphere Detector average detection throughput for $2\times 2$ MIMO                 |    |

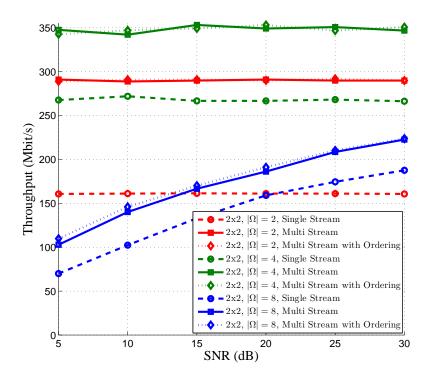

|             | obtained with single stream and multiple stream kernel executions                              | 70 |

| 4.17        | The Parallel Sphere Detector average detection throughput for $4{\times}4$ MIMO                |    |

|             | obtained with single stream and multiple stream kernel executions                              | 71 |

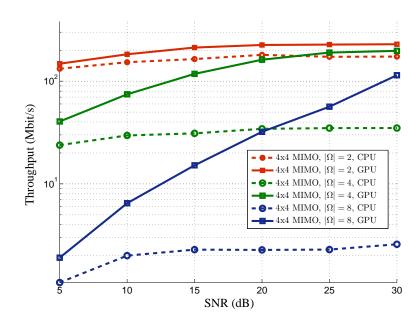

| 4.18        | The comparison of the average detection throughput of (i) the Parallel                         |    |

|             | Sphere Detector algorithm implemented on a GP-GPU architecture and                             |    |

|             | (ii) the sequential Sphere Detector executed on every thread of a multi-                       |    |

|             | core CPU                                                                                       | 72 |

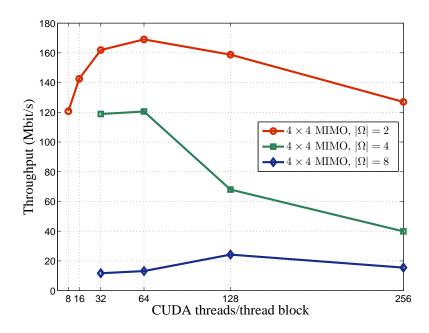

| 4.19        | The Parallel Sphere Detector average detection throughput for $4{\times}4$ MIMO                |    |

|             | obtained at 20 dB SNR with single stream kernel execution and multiple $$                      |    |

|             | thread block configurations                                                                    | 73 |

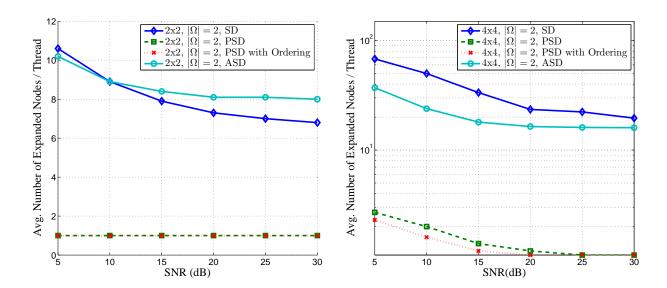

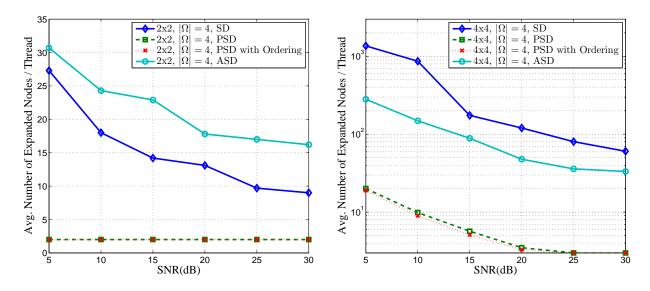

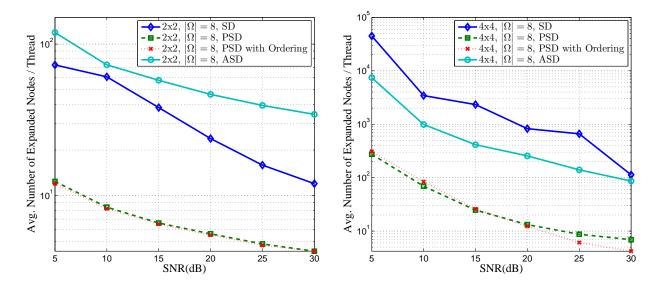

| 4.20        | Comparison of the average number of expanded nodes per thread for (a)                          |    |

|             | $2\times 2,$ (b) $4\times 4$ MIMO and $ \Omega =2$ for the sequential, parallel and automatic  |    |

|             | Sphere Detector algorithms                                                                     | 74 |

| 4.21        | Comparison of the average number of expanded nodes per thread for (a)                          |    |

|             | $2\times 2$ , (b) $4\times 4$ MIMO and $ \Omega =4$ for the sequential, parallel and automatic |    |

|             | Sphere Detector algorithms                                                                     | 75 |

| 4.22        | Comparison of the average number of expanded nodes per thread for (a)                          |    |

|             | $2\times 2,$ (b) $4\times 4$ MIMO and $ \Omega =8$ for the sequential, parallel and automatic  |    |

|             | Sphere Detector algorithms                                                                     | 75 |

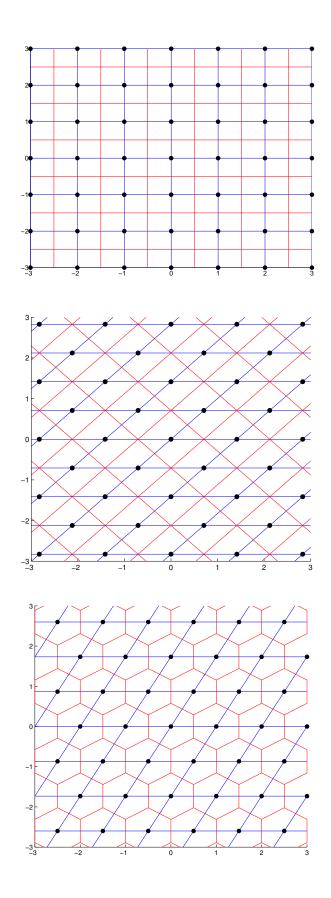

| 5.1         | Square, rhombic and hexagonal lattices with the fundamental parallelo-                         |    |

| 0.1         | tope structures (blue) and the Voronoi regions (red)                                           | 87 |

| 5.2         | The cumulative distribution function of the condition number $\kappa(\tilde{\mathbf{B}})$ and  | 0. |

| J. <u>J</u> | orthogonality defect $\xi(\tilde{\mathbf{B}})$ after Lenstra-Lenstra-Lovász and Seysen lattice |    |

|             | reduction for $16 \times 16$ zero-mean, unit variance Gaussian random matrices.                | 98 |

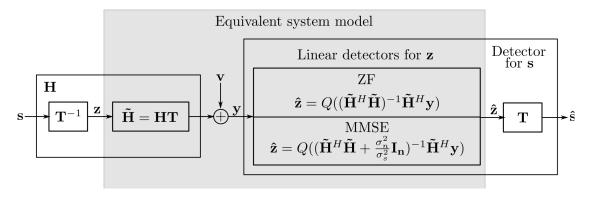

| 5.3         | Equivalent system model of lattice reduction aided MIMO detection                              | 99 |

| J . J       | = qualitative operation and act of involve foundation and a fitting decoupling to the          | 00 |

| 5.4  | Bit error rate of lattice reduction aided linear detectors for $4 \times 4$ MIMO  |     |

|------|-----------------------------------------------------------------------------------|-----|

|      | systems with 16-QAM symbol constellation                                          | 101 |

| 5.5  | Average uncoded bit error rate per subcarrier for $64 \times 64$ MIMO systems     |     |

|      | with 4-QAM symbol constellation                                                   | 104 |

| 5.6  | Average uncoded bit error rate per subcarrier for $128 \times 128$ MIMO systems   |     |

|      | with 4-QAM symbol constellation                                                   | 104 |

| 5.7  | The high-level work distribution among the GP-GPU threads and the                 |     |

|      | mapping of the size reduction, inner product and column swap operations           |     |

|      | for the Cost-Reduced All-Swap LLL lattice reduction algorithm                     | 110 |

| 5.8  | Kernels scheduling on a dynamic parallelism enabled GP-GPU for the                |     |

|      | Modified-Block LLL lattice reduction algorithm                                    | 114 |

| 5.9  | Kernels scheduling on the heterogeneous platform for the Cost-Reduced             |     |

|      | Modified-Block LLL lattice reduction algorithm                                    | 116 |

| 5.10 | Computational time of Cost-Reduced All-Swap LLL and Modified-Block                |     |

|      | LLL lattice reduction algorithms with different block sizes ranging from          |     |

|      | $2-2^9$ for square matrices of dimensions $2^3-2^{10}$                            | 117 |

| 5.11 | Computational time of the Modified-Block LLL lattice reduction algo-              |     |

|      | rithm with optimal block size $l$ on different architectures                      | 118 |

| 5.12 | Computational time of Cost-Reduced All-Swap LLL lattice reduction al-             |     |

|      | gorithm for matrix dimensions $2^3-2^6$ on 1 and 2 $\times$ Tesla K20, GeForce    |     |

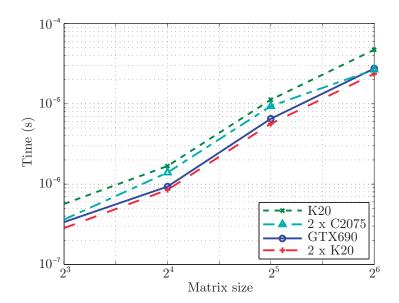

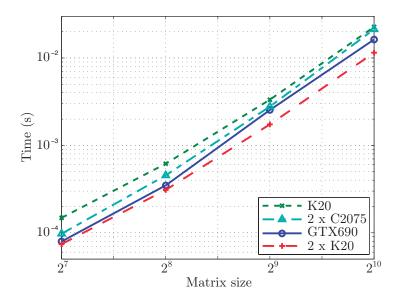

|      | GTX690 and 2 $\times$ Tesla C2075 GP-GPU configurations                           | 119 |

| 5.13 | Computational time of Cost-Reduced All-Swap LLL lattice reduction al-             |     |

|      | gorithm for matrix dimensions $2^7-2^{10}$ on 1 and 2 $\times$ Tesla K20, GeForce |     |

|      | GTX690 and 2 $\times$ Tesla C2075 GP-GPU configurations                           | 119 |

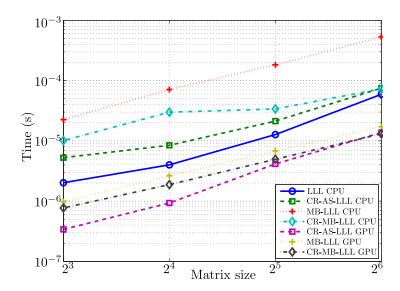

| 5.14 | Computational time of the LLL, Cost-Reduced All-Swap LLL, Modified-               |     |

|      | Block LLL and Cost-Reduced Modified-Block LLL algorithms for matrix               |     |

|      | dimensions $2^3 - 2^6$                                                            | 120 |

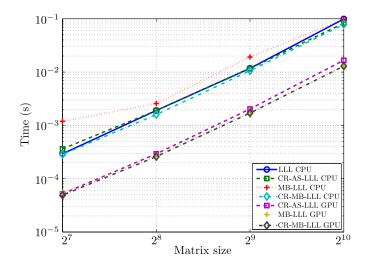

| 5.15 | Computational time of the LLL, Cost-Reduced All-Swap LLL, Modified-               |     |

|      | Block LLL and Cost-Reduced Modified-Block LLL algorithms for matrix               |     |

|      | dimensions $2^7 - 2^{10}$                                                         | 191 |

# List of Tables

| 4.1 | Definition of parameters used in the Parallel Sphere Detector algorithm | 53  |

|-----|-------------------------------------------------------------------------|-----|

| 4.2 | Valid Parallel Sphere Detector algorithm parameter configurations       | 56  |

| 4.3 | Algorithmic comparison of the Parallel Sphere Detector with the sequen- |     |

|     | tial Sphere Detector algorithm                                          | 59  |

| 4.4 | Main characteristics of the GK104 Kepler architecture                   | 68  |

| 4.5 | Parallel Sphere Detector algorithm parameter configurations achieving   |     |

|     | highest detection throughput with multiple stream kernel executions for |     |

|     | $2\times 2$ and $4\times 4$ MIMO systems at 20 dB SNR                   | 69  |

| 4.6 | Parallel Sphere Detector algorithm parameter configurations achieving   |     |

|     | highest detection throughput for different number of CUDA threads and   |     |

|     | single stream kernel execution for $4\times4$ MIMO systems at 20 dB SNR | 73  |

| 4.7 | Throughput comparison of existing MIMO detector algorithms              | 77  |

| 5.1 | Lattice reduction aided precoding algorithms                            | 103 |

| 5.2 | The comparison of the GTX690, K20 and C2075 GP-GPU architectures        | 118 |

| 5.3 | Performance comparison of the Cost-Reduced All-Swap LLL and the Cost-   |     |

|     | Reduced Modified-Block LLL algorithms with existing lattice reduction   |     |

|     | implementations                                                         | 122 |

# List of Algorithms

| 1  | Zero-Forcing Vertical BLAST detection algorithm                                                    |

|----|----------------------------------------------------------------------------------------------------|

| 2  | Sphere Detector algorithm for estimating $\mathbf{s}_{ML} = (s_1, s_2, \cdots, s_N)$ 36            |

| 3  | The Automatic Sphere Detector algorithm                                                            |

| 4  | K-Best SD algorithm for estimating $\mathbf{s} = (s_1, s_2, \dots, s_N)$ 46                        |

| 5  | High-level overview of the Parallel Sphere Detector algorithm 54                                   |

| 6  | Parallel Sphere Detector algorithm for estimating $\mathbf{s}_{ML} = (s_1, s_2, \cdots, s_N)$ . 58 |

| 7  | Hermite-Korkin-Zolotareff lattice reduction algorithm 94                                           |

| 8  | The Lenstra-Lenstra-Lovász lattice reduction algorithm 95                                          |

| 9  | Seysen's lattice reduction algorithm                                                               |

| 10 | The Cost-Reduced All-Swap LLL lattice reduction algorithm 108                                      |

| 11 | The pseudocode of the Cost-Reduced All-Swap LLL CUDA kernel - pro-                                 |

|    | cessing of one lattice basis $\mathbf{B}_i$ with a two dimensional thread block con-               |

|    | figuration $TB(T_x, T_y)$                                                                          |

| 12 | The OpenMP pseudocode of the Cost-Reduced All-Swap LLL lattice re-                                 |

|    | duction algorithm                                                                                  |

| 13 | The Modified-Block LLL lattice reduction algorithm                                                 |

| 14 | The mapping of the Cost-Reduced Modified-Block LLL lattice reduction                               |

|    | algorithm to a heterogeneous platform                                                              |

## Chapter 1

## Introduction

#### 1.1 Motivation and scope

The most important driving forces in the development of wireless communications are the need for higher link throughput, higher network capacity and improved reliability. The limiting factors of such systems are equipment cost, radio propagation conditions and frequency spectrum availability. The ever increasing need for higher transmission rates motivated researchers to develop new methods and algorithms to reach the Shannon capacity limit of single transmit and receive antenna wireless systems. Research in information theory [8] has revealed that important improvements can be achieved in data rate and reliability when multiple antennas are applied at both the transmitter and receiver sides, referred to as MIMO systems [9]. The performance of wireless systems is improved by orders of magnitude at no cost of extra spectrum use.

The complexity of MIMO detectors used over different receiver structures depends on many factors, such as antenna configuration, modulation order, channel, coding, etc. In order to achieve optimal BER for Additive White Gaussian Noise (AWGN) channels ML detection has to be performed. The exhaustive search implementation of ML detection has a complexity that grows exponentially with both the number of elements in the signal set and the number of antennas, thus, this technique is not feasible in real systems. The SD seems to be a promising solution to significantly reduce the search space. The fundamental aim of the SD algorithm is to restrict the search to lattice points that lie within a certain sphere around a given received symbol vector. Reducing the search space will not affect the detection quality, because the closest lattice point inside the sphere will also be the closest lattice point for the whole lattice. The drawbacks of the SD algorithm are: (i) the complexity still suffers of an exponential growth, when increasing

the number of antennas or the modulation order, (ii) the SD detection transforms the MIMO detection problem into a depth-first tree search that is highly sequential, and (iii) during every tree search several different paths have to be explored leading to a variable processing time.

When a multiple-antenna BS is applied to multi-user communication systems, spatial diversity can be achieved even if the MSs are not equipped with multiple antennas. However, since the MSs do not know other users' channels, the entire processing task must be done at the BS, especially symbol precoding to cancel multi-user interference. Assuming channel information is sent back by all the MSs to the BS, a promising technique that can be applied for both linear and non-linear precoding is the LR of the channel matrix [10], [11], [12], [13]. Furthermore, recent research [14], [15], [16], [17], [18] shows that the performance of linear and non-linear MIMO detectors can be improved when used in conjunction with LR techniques. The improved condition number and orthogonality defect of the reduced lattice basis achieves full diversity order even with less complex linear detection methods. However, the computational cost of LR algorithms depending on the lattice basis dimensions could be high, and can become critical for large MIMO arrays.

The computational complexity can grow extremely high when the optimal solution is required either for detection or precoding. However, during the research of different modulation schemes, channel models, precoding, detection and decoding techniques it might happen that the theoretical performance can be determined only by simulations. Another approach is to precondition or preprocess the problem, and afterwards, lower complexity signal processing algorithms (i.e. linear detection, precoding) can be performed. In this case, the complexity or the processing time is mostly influenced by the preprocessing algorithms. The conclusion of the above is that the price that has to be paid when using MIMO systems is the increased complexity of hardware components and signal processing algorithms and most of these algorithms can not be efficiently mapped to modern parallel architectures because of their sequential components.

Due to the major advances in the field of computing architectures and programming models the production of relatively low-cost, high-performance, MPAs such as GP-GPUs or Field Programmable Gate Arrays (FPGAs) was enabled. Research conducted in several scientific areas has shown that the GP-GPU approach is very powerful and offers a considerable improvement in system performance at a low cost [19]. Furthermore, market leading smartphones have sophisticated GP-GPUs, and high-performance GP-GPU

clusters are already available. Consequently, complex signal processing tasks can be offloaded to these devices. With these powerful MPAs the relatively high and variable computational complexity algorithms could be solved for real-time applications or they could speed-up the time of critical simulations.

The trend of using MPAs in several heavy signal processing tasks is visible. Computationally heavy signal processing algorithms like detection [20], [21], [22], [23], [24], [25], [26], decoding [27], [28] and precoding [29] are efficiently mapped on to GP-GPUs. Moreover, several GP-GPU based communication systems have been proposed in [30, 31]. An FPGA implementation of a variant of the LLL algorithm, the Clarkson's algorithm, is presented in [32]. In [33], a hardware-efficient Very Large Scale Integration (VLSI) architecture of the LLL algorithm is implemented, which is used for channel equalization in MIMO wireless communications. In [34], Xilinx FPGA is used for implementing LR-aided detectors, whereas [35] uses an efficient VLSI design based on a pipelined architecture.

The underlying architecture is seriously influencing the processing time and the quality of the results. Since the existing algorithms are mostly sequential, it is necessary to fundamentally redesign the existing algorithms in order to achieve peak performance with the new MPAs. By using these powerful devices new limits are reached, so in this thesis my goal is twofold: (i) to design efficient and highly parallel algorithms that solve the high complexity ML detection problem and (ii) to design and implement highly parallel preconditioning algorithms, such as lattice reduction algorithms, that enable afterwards the use of low complexity signal processing algorithms, achieving a near-optimal system performance.

#### 1.2 Thesis outline

The thesis is organized as follows. Chapter 2 discusses the Flynn's taxonomy of parallel architectures and gives a brief overview of the most important parallel programming models. Chapter 3 introduces the MIMO system model considered throughout the thesis and shows how MIMO can increase the spectral efficiency. Chapter 4 gives a comprehensive overview of MIMO detection methods and presents the newly introduced detection algorithm. Section 4.2 gives a classification of the MIMO detectors. Section 4.3 presents two fundamental low-complexity linear detectors and their performance is compared. Section 4.4 discusses the successive interference detection concept and gives a brief overview on the importance of detection ordering based on several metrics. Section 4.5 gives a theoretical investigation on the optimal ML detection. Section 4.5 describes

the SD algorithm together with a complexity analysis based on statistical methods, and the automatic SD is presented that gives the lower bound of node expansions during detection. Section 4.7 presents the most important non-ML tree-search based detectors. The presented algorithms served as a good basis to start the design of the PSD algorithm.

Section 4.8 introduces the new PSD algorithm. The precise details of **Thesis group** I. and II. are found in this section. The key concepts of the PSD algorithm are given in Sec. 4.8.1, its general description, together with an algorithmic comparison with the SD algorithm, is provided in Sec. 4.8.2, forming **Thesis I.a.** Parallel building blocks are designed in Sec. 4.8.3 for every stage of the PSD algorithm which facilitates the mapping to different parallel architectures, forming **Thesis I.b**. In Sec. 4.8.4 several levels of parallelism are identified and it is showed how CUDA kernels detect several symbol vectors simultaneously. Two computing load distribution strategies are presented and their application to a multi-stream GP-GPU environment is discussed. The achieved results in this section define Thesis I.c. Section 4.8.5 evaluates the performance of the PSD algorithm proposed by giving simulation results on the average detection throughput achieved, showing the distribution of work over the threads available and gives a comprehensive comparison with the results published in the literature. In Sec. 4.8.5.2 the effects of symbol ordering on the PSD algorithm are analyzed and the achieved performance enhancement is presented, forming **Thesis II.a.** Finally, Sec. 4.9 concludes the main results of this chapter.

Chapter 5 introduces LR and its applicability to MIMO systems, and new LR algorithms and their efficient mapping to parallel architectures are discussed. After giving the most important definitions, structures and limits in Sec. 5.2, the three fundamental LR algorithms are presented in Sec. 5.3. Section 5.4 shows how LR is applied to MIMO detection and multiple-input single-output (MISO) precoding, and the BER performance of low-complexity methods used in conjunction with LR is presented. Section 5.5 presents two parallelization strategies. The redesigned LR algorithms heavily rely on these methods.

Section 5.6 introduces my research in the field of parallel LR algorithms and their mapping to multi-core and many-core architectures. The precise details of **Thesis group III.** are found in this section. Section 5.6.1 presents the CR-AS-LLL algorithm and its mapping on to a GP-GPU architecture is given, forming **Thesis III.a**. In Sec. 5.6.2 it is shown how the block concept is applied in the case of large matrices and the resulting MB-LLL algorithm mapping is also discussed, **Thesis III.b.** is defined based on these results.

In Sec. 5.6.3 the complexity of the MB-LLL is further reduced, and the CR-MB-LLL is mapped to a heterogeneous platform where the efficient work scheduling of the CPU and GP-GPU is also discussed, **Thesis III.c.** is defined based on these results. Section 5.6.4 evaluates the performance of the new parallel algorithms on different architectures.

Finally, Chapter 6 presents the summary of the main results of my thesis.

## Chapter 2

# High-performance computing architectures and programming models

### 2.1 Flynn's taxonomy of parallel architectures

Parallel architectures are playing a prominent role in nowadays computing challenges. Modern supercomputers are built on various parallel processing units, thus, the classification of these architectures helps to get a better insight into the similarities and differences of the parallel architectures. When mapping an algorithm to a parallel architecture, or designing an application for a cluster, several levels of parallelism have to be identified and exploited. Instruction level parallelism is available when multiple operations can be executed concurrently. Loop level parallelism can be achieved when there is no data dependency between consecutive loop iterations. Procedure level parallelism can be achieved with the domain decomposition or the functional decomposition of the computational work. High-level parallelism is available when running multiple independent programs concurrently.

Flynn in [36], [37], [38] developed a methodology to classify general forms of parallel architectures along the two independent dimensions of *instruction stream* and *data stream*. Stream is defined as a sequence of instructions or data operated on by the computing architecture. The flow of instructions from the main memory to the CPU is the instruction stream, while the bidirectional flow of operands from the main memory, I/O ports to the CPU registers is the data stream. Flynn's taxonomy is a categorization of forms of parallel computer architectures. The most familiar parallel architectures are

categorized in four classes: (i) single instruction, single data (SISD) stream, (ii) single instruction, multiple data (SIMD) stream, (iii) multiple instruction, single data (MISD) stream and (iv) multiple instruction, multiple data (MIMD) stream.

The SISD class is implemented by traditional uniprocessors, i.e., CPUs containing only a single processing element (PE). During one clock cycle only one instruction stream is being processed and the input is provided by a single data stream. The concurrency achieved in these processors is achieved with the pipelining technique. The processing of an instruction is composed of different phases: (i) instruction fetch, (ii) decoding of the instruction, (iii) data or register access, (iv) execution of the operation, and (v) result storage. Since these phases are independent, the pipelining enables the overlapping of the different operations. However, the correct result is achieved if each instruction is completed in sequence. Scalar processors process a maximum of one instruction per cycle and execute a maximum of one operation per cycle. The next instruction is processed only after the previous instruction is completed and its results are stored. Superscalar processors decode multiple instructions in a cycle and use multiple functional units and a dynamic scheduler to process multiple instructions per cycle. This is done transparently to the user by analyzing multiple instructions from the instruction stream.

In the SIMD class the same instruction is executed by multiple PEs at every clock cycle, but each PE operates on a different data element. This is realized by broadcasting the same instruction from the control unit to every PE. The next instruction is only processed after every PE completed its work. This simultaneous execution is referred to as lock-stepping execution. The efficient data transfer from the main memory is achieved by dividing the main memory into several modules. Problems with a high degree of regularity, such as different matrix, vector operations, are best suited for these type of architectures. The common use of regular structures in many scientific problems makes SIMD architectures very effective in solving these problems. The SIMD class is implemented by array and vector processors.

An array processor consists of interconnected PEs with each having its own local memory space. There is possibility to access the global memory or the local memory of another PE, however, this has a high latency. By creating local interconnections of the PEs, a new level of shared memory can be defined that has a reduced latency, but its efficient use is implemented by simple and regular memory access patterns. Individual PEs could conditionally disable instructions in case of branching, entering in idle state.

A vector processor consists of a single processor that references a single global memory

Figure 2.1: The block diagram of the GK110 Kepler architecture.

Reprinted from [39].

space and has special functional units that operate specifically on vectors. The vector processor shows high similarities with SISD processors except that vector processors can treat data sequences, referred to as vectors, through their function units as a single entity. The sophisticated pipelining techniques, the high clock rate, and the efficient data transition to the input vector of these functional units achieve a significant throughput increase compared to scalar function units. An efficient algorithm mapping can hide the latency of the data loads and stores between the vector registers and main memory with computations on values loaded in the registers.

GP-GPUs employ the *single instruction*, *multiple threads* (SIMT) multi-threaded model. An application launches a number of threads that all enter the same program together, and those threads get dynamically scheduled onto a SIMD datapath such that threads that are executing the same instruction get scheduled concurrently. Figure 2.2 shows the Kepler GK110 architecture block diagram. The Kepler GK110 and GK210 implementations include 15 streaming multiprocessor (SMX) units and six 64-bit memory controllers.

Figure 2.2 shows the block diagram of the GK110 SMX architecture. Based on [39] the following components and features are available in the GK110/GK210 SMX units:

each of the Kepler GK110/210 SMX has 192 single-precision, 64 double-precision

CUDA cores, 32 special function units, and 32 load/store units;

Figure 2.2: The GK110/GK210 Kepler streaming multiprocessor (SMX) unit architecture.

#### Reprinted from [39].

- the SMX schedules threads in groups of 32 parallel threads called warps;

- each SMX has four warp schedulers and eight instruction dispatch units, allowing four warps to be issued and executed concurrently;

- Kepler's quad warp scheduler selects four warps, and two independent instructions per warp can be dispatched each cycle.

In the MISD class a single data stream is fed into multiple processing units and each PE has its own instruction stream. Thus, the number of control units is equal to the number of PEs. Only a few implementations of this class of parallel computer have ever existed. Problems that could be efficiently solved on these architectures are filter banks, i.e., multiple frequency filters operating on a single signal stream, or cryptography algorithms attempting to crack a single coded message.

Processors implementing the MIMD stream are said to be the parallel computers. Every PE has the possibility of executing a different instruction stream that is handled by a separate control unit and a data stream is available for every PE. The execution

Figure 2.3: The evolution of theoretical floating-point operations per second (FLOP/s) for CPU and GP-GPU architectures.

#### Reprinted from [40].

of different tasks can be synchronous or asynchronous (they are not lock-stepped as in SIMD processors), they can start or finish at different times. Usually, the solution of a problem requires the cooperation of the independently running processors, and this cooperation is realized through the existing memory hierarchy. By using shared memory or distributed shared memory the problem of memory consistency and cache coherency has to be solved. With the use of thread synchronization, atomic operations, critical sections the programmer can overcome these problems, however, there are problems that can be solved exclusively through hardware techniques. Todays multi-threaded processors, multi-core and multiple multi-core processor systems implement the MIMD class.

The above discussion showed that modern CPUs fall in the MIMD class, while the GP-GPUs implement a more flexible SIMD stream. Figure 2.3 gives an overview of the theoretical floating-point operations per second (FLOP/s) for different CPU and GP-GPU architectures. It can be seen that there is a huge potential in the GP-GPU architecture because the achievable theoretical FLOP/s is many times higher compared to the CPU architecture. However, in order to exploit this huge potential, the algorithm design has to take in consideration the limitations imposed by the SIMT architecture that is often a challenging task.

## 2.2 Overview of parallel programming models

A parallel programming model can be regarded as an abstraction of a system architecture. Thus, the program written based on a parallel programming model can be compiled and executed for the underlying parallel architecture. Because of the wide range of existing parallel systems and architectures different parallel programming models were created. A parallel programming model is general if the mapping of a wide range of problems for a variety of different architectures is efficient. The underlying memory architecture highly influences what parallel programming model is going to give a good abstraction. The three most fundamental parallel computer memory architectures are: shared memory, distributed memory and hybrid distributed-shared memory.

In shared memory parallel computers the processors share the same memory resources, thus, there is only a single memory address space. Cache coherency is available, meaning that every memory update is visible to every processor. Shared memory computers can be further classified as: uniform memory access (UMA) and non-uniform memory access (NUMA) computers. The UMA model is implemented by symmetric multiprocessor (SMP) computers, where identical processors are placed near the shared memory, thus, the memory access time is equal to every processor. The NUMA model is implemented by linking several SMPs and every SMP can directly access the memory of another SMP. However, in this case the memory access time is different for processors lying in different SMPs. The advantages of this model are the global address space and fast data-sharing. The main disadvantages are the lack of scalability and the need of synchronization in order to ensure data correctness.

The distributed memory architecture model is encountered in networked or distributed environments such as clusters or grids of computers. In this case every processor operates independently and has its own local memory, thus, there is no global memory address space. No cache coherency is present, so the memory change of one processor does not effect the memory of other processors. The programmer's task is to manage the data communication and the synchronization of different tasks. The advantage of this approach is that each processor can rapidly access its own memory because no overhead is required to assure global cache coherency, and the memory can easily scale with the number of processors. Among the disadvantages of this model is the non-uniform memory access time and the burden to manage the data communication between processors.

Nowadays, systems implementing the hybrid distributed-shared memory model are the largest and fastest computers. In this model multiple shared memory processors are connected through a network resulting in a distributed architecture. The hybrid model can be further improved by adding GP-GPUs to the shared memory architecture. This is a very powerful model, however, the programming complexity is significantly increased. Thus, in order to exploit the benefits of this hybrid model efficient algorithm mapping, computational load balancing and communication organization has to be designed.

The two predominant parallel programming models using pure shared or distributed memory approach are the *Open Multi-Processing* (OpenMP) [41] for shared memory and the *Message Passing Interface* (MPI) [42] for distributed memory systems. In addition, with the advent of the massively parallel many-core GP-GPUs new programming models like CUDA [40] and *Open Computing Language* (OpenCL) [43] were introduced.

OpenMP is a high-level abstraction of shared memory systems. OpenMP is implemented as a combination of a set of compiler directives, pragmas, and a runtime providing both management of the thread pool and a set of library routines. With the help of the directives the compiler is instructed to spawn new threads, to perform shared memory operations, to perform synchronization operations, etc. The fork-join threading model is used to switch between sequential and parallel operation modes. During a fork operation a thread splits into several threads, thus, the execution branches off in parallel, and after their task is completed they are joined resuming to sequential execution.

MPI is a parallel programming model for distributed memory systems and facilitates the communication between processes by interchanging messages. The communication is cooperative and occurs only when the first process executes a send operation and the second process executes a receive operation. The task of the programmer is to manage the workload by defining what tasks are to be performed by each process.

Since massively parallel many-core GP-GPUs are playing an important role in this thesis, in Sec. 2.2.1 the most important definitions and components of CUDA are presented.

#### 2.2.1 The CUDA programming model

The programming of GP-GPU devices has became popular since Nvidia published the CUDA parallel programming model. Traditional CPUs are able to execute only a few threads, but with relatively high clock rate. In contrast, GP-GPUs have a parallel architecture that support the execution of thousands of threads with a lower clock-rate.

An extensive description of CUDA programming and optimization techniques can be found in [40]. The main entry points of GP-GPU programs are referred to as *kernels*.

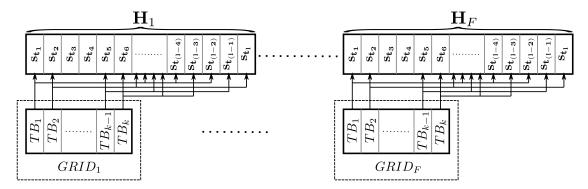

These kernels are executed N times in parallel by N different *CUDA threads*. CUDA threads are grouped in *thread blocks* (TBs). The number of threads in a TB is limited, however, multiple equally-shaped TBs can be launched simultaneously. A *grid* is a collection of TBs. The threads in the TB or the TBs in the grid can have a one-dimensional, two-dimensional or three-dimensional ordering.

The cooperation between the threads is realized with the help of multiple memory spaces that differ in size, latency and visibility. In CUDA the following hierarchy of memory levels are defined: (i) private, (ii) shared, (iii) global, (iv) constant and (v) texture memory.

In some cases specific threads have to wait for the results generated by other threads. Therefore, threads within a TB can be *synchronized*. In order to continue the execution, each thread has to reach the synchronization point. There is no similar mechanism to synchronize TBs in a grid. When a kernel finishes its execution it can be regarded as a global synchronization of the TBs.

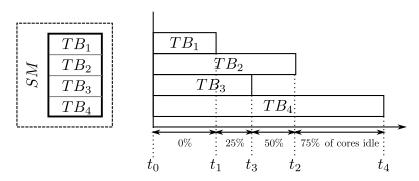

The Nvidia GP-GPU architecture is built around a scalable array of multithreaded streaming multiprocessors (SMs). The TBs of the grid are distributed to the SMs with available execution capacity by the grid management unit. An important metric of the SMs usage is occupancy. The occupancy metric of each SM is defined as the number of active threads divided by the maximum number of threads. Groups of 32 threads, called warps, are executed together. The maximum number of TBs running simultaneously on a multiprocessor is limited by the maximum number of warps or registers, or by the amount of shared memory used by the kernel.

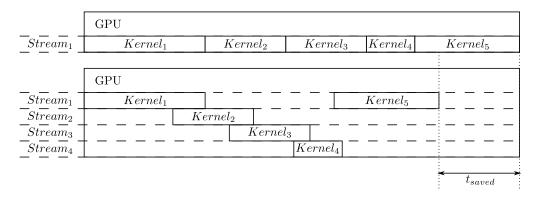

In order to concurrently execute hundreds of threads, the SMs employ a SIMT architecture. A warp executes one common instruction at a time. In the case of branching, the warp will serially execute each branch path. In order to achieve full efficiency, divergence should be avoided. Applications manage concurrency through *streams*. A stream is a sequence of commands that are executed in order. Different streams may execute their commands out of order with respect to one another or concurrently. Thus, launching multiple kernels on different streams is also possible. This can be very efficient when kernels can be launched independently from each other.

## Chapter 3

## Overview of MIMO

## communications

#### 3.1 Benefits of MIMO systems

The key feature of MIMO systems is the ability to turn multipath propagation, traditionally a pitfall of wireless transmissions, into a benefit for the user, thus, the performance of wireless systems is improved by orders of magnitude at no cost of extra spectrum use. The performance enhancements of MIMO systems are achieved through array gain, spatial diversity gain, and spatial multiplexing gain.

Array gain is defined as the efficient combination of the transmitted or received signals that result in the increase of the signal-to-noise ratio (SNR). As a result the noise resistance and the coverage of a wireless network is improved. Array gain is exploited by methods like: selection combining, maximal-ratio combining, equal-gain combining as discussed in [44].

In case of spatial diversity different representations of the same data stream (by means of coding) is transmitted on different parallel transmit branches, i.e., it introduces controlled redundancy in both space and time. At the receiver side independent copies of the same transmitted signal are encountered because of the rich scattering environment. If a signal path experiences a deep fade the original signal still can be restored, thus, the probability of error is minimized. The number of copies received is referred to as the diversity order. A MIMO channel with n transmit antennas and m receive antennas potentially offers  $n \cdot m$  independent fading links, and hence a spatial diversity order of  $n \cdot m$ . Space-time coding (STC) was introduced to support transmit diversity in [45], [46], [47], [48].

Figure 3.1: MIMO system architecture with n transmitter and m receiver antennas.

Spatial multiplexing focuses on maximizing the capacity of a radio link by transmitting independent data streams on different transmit branches simultaneously and within the same frequency band. In a rich scattering environment, the receiver can separate the data streams and since each data stream experiences the same channel quality as a single-input single-output (SISO) system, the capacity is increased by a multiplicative factor equal to the number of streams. Spatial multiplexing was exploited in the following works [129], [49], [8].

In hybrid MIMO configurations the benefits of spatial multiplexing and space-time coding schemes are combined. This is achieved by dividing the transmit antennas into sub-groups where each sub-group is space-time coded independently. At the receiver group spatial filters are used followed by space-time decoding. For a few good examples refer to [50], [51] and [52].

# 3.2 MIMO system model

A MIMO system consists of n transmit and m receive antennas as shown in Fig. 3.1. The transmit antennas are sending a complex signal vector  $\tilde{\mathbf{s}}_t$  of size n during one symbol period. The received complex symbol vector  $\tilde{\mathbf{y}} = (\tilde{y}_1, \tilde{y}_2, ..., \tilde{y}_m)^T$  is expressed as

$$\tilde{\mathbf{y}} = \tilde{\mathbf{H}}\tilde{\mathbf{s}}_t + \tilde{\mathbf{v}} \tag{3.1}$$

where  $\tilde{\mathbf{v}} = (\tilde{v}_1, \tilde{v}_2, ..., \tilde{v}_m)^T$  is the additive channel noise and the superposition of the transmitted symbols is modeled by the channel matrix  $\tilde{\mathbf{H}} \in \mathbb{C}^{m \times n}$ . The statistical prop-

erties of the MIMO system model are summarized as follows:

- the noise vector is modeled as  $\tilde{\mathbf{v}} \sim \mathcal{CN}(0, \mathbf{K})$  zero-mean, circularly-symmetric jointly-Gaussian complex random vector, with covariance matrix  $\mathbf{K} = \sigma^2 \mathbf{I}_m$  and uncorrelated components are assumed,

- the elements  $\tilde{h}_{ij} \sim \mathcal{CN}(0,1)$  of the channel matrix  $\tilde{\mathbf{H}}$  are assumed to be i.i.d. zero-mean, complex circularly-symmetric Gaussian variables with unit variance,

- the transmitted symbols are modeled as independent and identically distributed (i.i.d.) random variables which are uniformly distributed over a symbol set  $\tilde{\Omega}$ , moreover it is assumed that the symbol set is centered at zero  $E\left\{\tilde{\mathbf{s}}_{t}\right\}=0$  and the average transmit power of each antenna is normalized to one, i.e.  $E\left\{\tilde{\mathbf{s}}_{t}\tilde{\mathbf{s}}_{t}^{H}\right\}=\mathbf{I}_{n}$ .

The elements of the symbol set  $\tilde{\Omega}$  are drawn from an  $M_c$ -ary Quadrature Amplitude Modulation (M-QAM) constellation usually employed in MIMO communications, where  $M_c$  stands for the number of constellation points and typically  $M_c = 4, 16, 64$ . As a result the elements of the symbol set are defined as

$$\tilde{\Omega} = \{ a + bi, a, b \in \mathbb{D} \}, \tag{3.2}$$

where

$$\mathbb{D} = \left\{ \pm \frac{1}{2} a, \pm \frac{3}{2} a, \dots, \pm \frac{\sqrt{M_c} - 1}{2} a \right\} \text{ and } a = \sqrt{\frac{6}{M_c - 1}}.$$

(3.3)

The parameter a is used for normalizing the power of the transmit signals to 1. The components of  $\tilde{\mathbf{s}}_t = (\tilde{s}_1, \tilde{s}_2, ..., \tilde{s}_n)^T$  are drawn from  $\tilde{\Omega}$ , i.e.  $\tilde{\mathbf{s}}_t \in \tilde{\Omega}^n$ , and carry  $\log_2 M_c$  Gray-encoded bits each. Block-fading channel is assumed where the channel matrix remains quasi-static within a fading block, but it is independent between successive fading blocks. Furthermore, it is assumed that the channel matrix is known by the receiver, it has been estimated before without errors.

The original complex representation of the system model, presented in Eq. 3.1, can be transformed into an equivalent real-valued model at the cost of increasing its dimension, as follows:

$$\mathbf{y} = \mathbf{H}\mathbf{s}_t + \mathbf{v},\tag{3.4}$$

where

$$\mathbf{y} = \begin{pmatrix} \Re(\tilde{\mathbf{y}}) \\ \Im(\tilde{\mathbf{y}}) \end{pmatrix}_{M \times 1}, \mathbf{s}_{t} = \begin{pmatrix} \Re(\tilde{\mathbf{s}}_{t}) \\ \Im(\tilde{\mathbf{s}}_{t}) \end{pmatrix}_{N \times 1}, \mathbf{v} = \begin{pmatrix} \Re(\tilde{\mathbf{v}}) \\ \Im(\tilde{\mathbf{v}}) \end{pmatrix}_{M \times 1}, \mathbf{H} = \begin{pmatrix} \Re(\tilde{\mathbf{H}}) & -\Im(\tilde{\mathbf{H}}) \\ \Im(\tilde{\mathbf{H}}) & \Re(\tilde{\mathbf{H}}) \end{pmatrix}_{M \times N}$$

(3.5)

and where M=2m and N=2n. In the transformed MIMO system model  $\mathbf{y},\mathbf{H},\mathbf{s}_t$  are all real-valued quantities and  $\Omega=\mathbb{D}$  is a real-valued signal set.

# 3.3 MIMO capacity

The notion of channel capacity was introduced by Shannon in [53]. The capacity of a channel, denoted by C, is the maximum rate at which reliable communication can be performed, and is equal to the maximum mutual information between the channel input and output vectors. Shannon proved two fundamental theorems: (i) for any rate R < C and any desired non-zero probability of error  $P_e$  there exists a rate R code that achieves  $P_e$  and (ii) the error probability of rates R > C higher then the channel capacity is bounded away from zero. As a result, the channel capacity is a fundamental limit of communication systems.

Several channel capacity definitions are available in the literature depending on: (i) what is known about the state of the channel, referred to as channel state information (CSI), or the distribution of the channel, referred to as channel distribution information (CDI), and the time scale of the fading process. For a time-varying channel where CSI is available at both the transmitter and receiver, namely the channel matrix  $\hat{\mathbf{H}}$  is known, the transmitter can adapt its rate or power based on the CSI. In this case the ergodic capacity is defined as the maximum mutual information averaged over all the channel states. Ergodic capacity is a relevant metric for quickly varying channels, since the channel experiences all possible channel states over the duration of a codeword. In case of perfect CSI at both the transmitter and receiver the *outage capacity* is defined as the maximum rate of reliable communication at a certain outage probability. Outage capacity requires a fixed data rate in all non-outage channel states and no data is transmitted when the channel is in outage since the transmitter knows this information. Outage capacity is the appropriate capacity metric in slowly varying channels, where the channel coherence time exceeds the duration of a codeword, thus each codeword is affected by only one channel realization.

In the following the capacity of single-user MIMO channel is considered for the case

when: (i) CSI is available at the transmitter (CSIT) and receiver (CSIR) and the channel is constant, and (ii) CDIT and CSIR is available and fading channel is assumed.

When CSIT is available the estimated distribution or channel state is sent to the transmitter through a feedback channel. If the transmitter adapts to these time-varying short-term channel statistics then capacity is increased relative to the transmission strategy associated with just the long-term channel statistics. The average transmit power is constrained across all transmit antennas as  $E[\tilde{\mathbf{s}}_t^H \tilde{\mathbf{s}}_t] \leq P$ . When the channel is constant, and CSIT, CSIR is available, the capacity is defined as

$$C = \max_{\tilde{\mathbf{Q}}: tr(\tilde{\mathbf{Q}}) = P} \log \det(\mathbf{I}_m + \tilde{\mathbf{H}} \tilde{\mathbf{Q}} \tilde{\mathbf{H}}^H)$$

(3.6)

where  $\tilde{\mathbf{Q}}$  is the input covariance matrix, which is  $n \times n$  positive semi-definite complex matrix.

With the help of the singular value decomposition (SVD) the channel matrix can be factorized as

$$\tilde{\mathbf{H}} = \tilde{\mathbf{U}} \mathbf{\Sigma} \tilde{\mathbf{V}}^H, \tag{3.7}$$

where  $\tilde{\mathbf{U}}$  is  $\mathbb{C}^{m \times m}$  unitary matrix,  $\mathbf{\Sigma}$  is  $\mathbb{R}^{m \times n}$  diagonal matrix with real non-negative entries, and  $\tilde{\mathbf{V}}$  is  $\mathbb{C}^{n \times n}$  unitary matrix. The diagonal elements of matrix  $\mathbf{\Sigma}$ , denoted by  $\sigma_i$ , are the singular values of  $\tilde{\mathbf{H}}$  and a descending order is assumed  $\sigma_1 \geq \sigma_2 \geq \cdots \geq \sigma_{\min(n,m)}$ . The matrix  $\tilde{\mathbf{H}}$  has exactly r positive singular values, where r is the rank of  $\tilde{\mathbf{H}}$ , and  $r \leq \min(n,m)$ . In [44], [8] it was shown that the SVD can convert channel  $\tilde{\mathbf{H}}$  into  $\min(n,m)$  parallel, noninterfering SISO channels after precoding the input, i.e.  $\bar{\mathbf{s}}_t = \tilde{\mathbf{V}}\tilde{\mathbf{s}}_t$ , and the received vector is multiplied by matrix  $\tilde{\mathbf{U}}^H$ , resulting in  $\bar{\mathbf{y}} = \tilde{\mathbf{U}}^H\tilde{\mathbf{y}}$ . The system model is transformed as

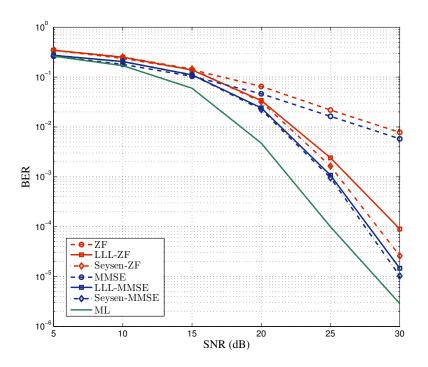

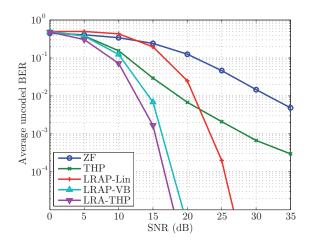

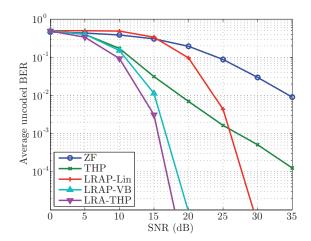

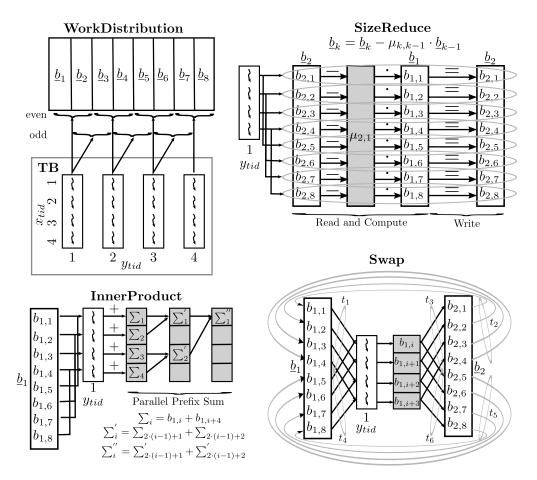

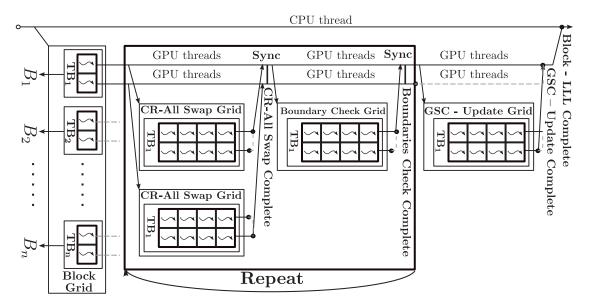

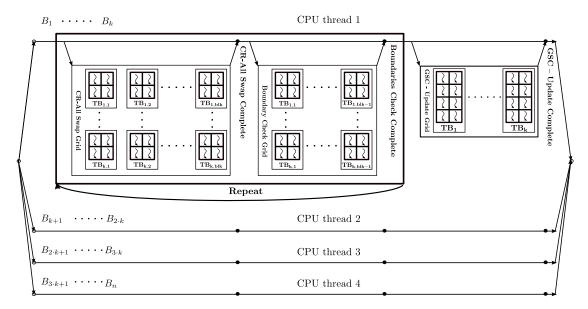

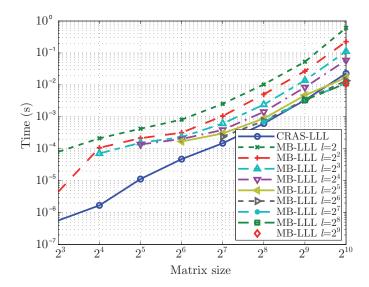

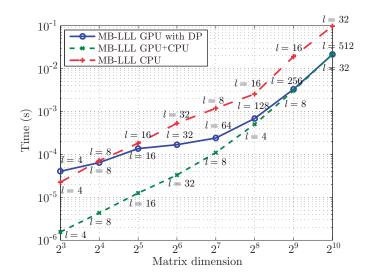

$$\overline{\mathbf{y}} = \widetilde{\mathbf{U}}^{H} (\widetilde{\mathbf{H}} \overline{\mathbf{s}}_{t} + \widetilde{\mathbf{n}})$$